例如,针对服务器的Nehalem处理器将拥有至少4组QPI传输,可至少组成包括4枚处理器的4路高端服务器系统(也就是16枚运算内核至少32线程并行运作)。而且在多处理器作业下,每颗处理器可以互相传送资料,并不需经过芯片组,从而大幅提升整体系统性能。随着未来Nehalem架构的处理器集成内存控制器、PCI-E 2.0图形接口乃至图形核心,QPI架构的优势将进一步发挥出来。

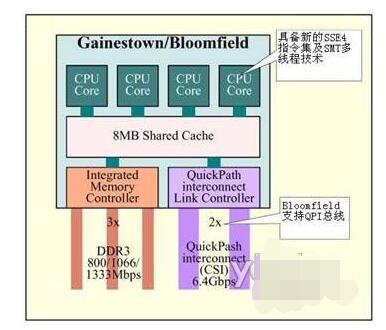

为了降低QPI总线的延迟,Intel打算在4路处理器以上的系统中使用一种叫做粘贴缓存的技术。它主要是倚靠更大容量的二级高速缓存来存储南桥和北桥的数据,使处理器不必反复通过QPI总线来读取南北桥信息。同时,为了更高提升数据处理效率,英特尔还将在处理器内部集成内存控制器(IMC)。QPI和IMC结合,可以让Intel更轻松地扩展多路系统和高性能计算(HPC)应用,而Intel现有的处理器架构更关注于指令执行引擎和缓存架构,以便在单线程应用中提高性能,导致双路服务器平台性能受限,也无法在对内存带宽需求甚高的HPC中发挥作用。对于第一代采用QPI总线的Nehalem Xeon来说,集成了3通道的DDR3内存控制器,这样在搭配DDR3 1066的情况下,每个处理器自己就能得到25.6GB/s的内存带宽,大概是现在Tigerton系统的5倍,并且这个带宽数量随着处理器插座的增长而增长,对于四插座系统,总的带宽将增长到恐怖的102.4GB/s。强大的内存性能将保证即使每个插座上边采用8核心的处理器,内存带宽也不会成为性能发挥的瓶颈。需要说明的是在QPI中,对于四路系统来说,任何两个处理器之间都可以直接通信,这样,一个处理器可以很方便的访问到其他处理器控制的内存,这可以大大提升效率。另外,由于在QPI系统下不同处理器可以直接通信,同步缓存称为很方便的事情,再也不用通过北桥的内存读写来进行了。

结语:

随着QPI的正式推出,英特尔主导的QPI及AMD的HT 两大未来总线系统将会正面冲突。为了让多核心的系统更高效的工作,我们相信今后的芯片组会更加复杂,多条系统总线连接才是今后系统总线发展的王道。需要说明的是,英特尔在季秋IDF是已经在展示了可以工作的、首个采用QPI互联架构的Nehalem平台。我们有理由相信,QPI将冲破内存性能带来的樊篱,实现性能的新飞跃。

关于接口,总线,驱动就介绍完了,您有什么想法可以联系小编。