现代芯片验证领域,无例外地也出现了类似状况。大量新方法、新模型、新类库,不断涌现,减轻了验证工程师们重复开发底层代码的负荷,将更多精力投入到实际项目上。这一套新思路中,主要构成部分便是验证语言(如Vera、SystemVerilog)、验证基本库(RVM、VMM),和相应的验证模型(Verification IP)。

3.VMM的应用

VMM不仪是方法学,更是该方法的具体实现。它包括一系列的类库(class library)、类对象(ob-ject)联接关系,以及用户定制的代码。

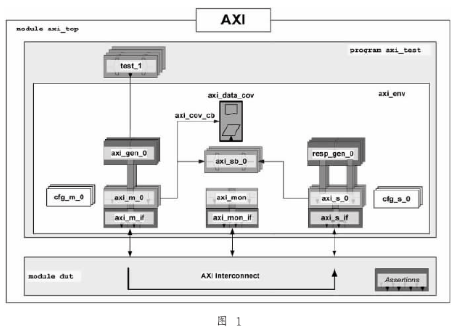

如图1所示的测试平台中,各部件(component),或即对象,是VMM基本类/扩展类的实例化(Instantiate)。所涉及到的VMM基本类有vmm_xactor、vmm_scenario_gen和vmm_data等。

联接各部件,构成一个整体还需要其他一些基本类,包括vmm_env、vmm_channel以及vmm_xactor_callbacks等。

除此之外,用户要根据芯片的实际状况,添加或修改约束条件(constraint)、接口联线(interface)、执行步骤、覆盖率定义和自动比对机制(au-to-check)。

3.1 背景

该种类型的验证平台充分利用了软件工程的成果,将整个测试平台按照所实现的功能,分门别类予以切割,实现各模块独自开发、分别维护。

目前,芯片规模趋于庞大,协议愈形复杂,通常要传递海量数据,并拥有数目繁多的端口。如果还以先前纯Verilog的方式建立验证系统,将很难满足芯片开发、投片的进度。

极而言之,简单地激励DUT输入端口、监控相应的输出端口和编写临时性的代码来做数据比对,这种验证方法已相当落后了。当然,我们也看到:对某些结构简单的芯片还有一定市场,纯粹Verilog语言的验证平台也可以做到非常复杂(但是,很难维护),并且学习面向对象编程的代价容易令人望而却步。但这些都是主流之外的个例,故对此本文不深入展开。

现代验证系统,尽管包含数量众多的模块、多样的数据类型/协议及各模块间复杂的信息传递(保持同步、共享数据等),它仍然是继承传统方法,归纳以往的验证经验,依照惯常的步骤建立测试平台。

VMM方法也概莫能外。依照通常的流程,它为所有应用VMM的测试平台,设定了九个步骤,定义在 vmm_env 中 :gen_cfg、build、reset_dut、cfg_dut、start、wait_for_end、stop、cleanup和report。

另一方面,VMM平台的架构,按抽象层次划分,由以下部件组成:测试例(Test)、场景发生器(gen-erator)、驱动部件(driver)、监控部件(monitor)、数据比对部件(scoreboard)、数据对象(data objects)、数据传输管道(channel)、回调函数集(callbacks)、配置总集(dut_cfg与sys_cfg)、覆盖率统计部件,和联接并集成以上所有部件的环境对象(environmentobject),如图2所示。