CEI-P编码采用帧同步取代定位同步。64B66B采用同步比特实现定位,而CEI-P将24个64比特码字看作一帧,这样用1个比特就可以实现数据或控制字符的判定。附加的24比特用于误码校验与信令。其中误码校验使用20比特,采用fire-code技术,可以纠正长达7比特的突发误码串。

10GBase-KR编码技术。这种技术的系统开销与CEI-P一致,都是3%,主要的不同在于帧的长度是32个码字,而不是24个码字。这样一来纠错码长度就是32比特,可以纠正比CEI-P更长的突发误码串。而它采用的扰码规则与10GbE相似。只不过它的扰码多项式与10GBase-R一致,寄存器采用的初始序列为“010101……”,而且每一帧重置一次。

Interlaken PHY编码技术。Interlaken编码技术的系统开销为4.5%(64/67)。它的码字基于64比特。与其它低开销编码技术相比,Interlaken的主要不同之处在于:

同步信号为3个比特,其中两个比特用于区分数据与控制,一个比特用于标识数据是否转化。数据转化比特的目的与8B10B类似,都是为了保证直流平衡;

Interlaken采用与10GbE相同的边扰码特征多项式实现扰码。这样可以避免因采用自同步扰码器所导致的误码复制问题。一个同步码字用于传递扰码器状态,而且它非常长的扰码长度保证不会出现很长的连“0”或者连“1”;

整个链路采用CRC32循环冗余校验方式保证误码校验。

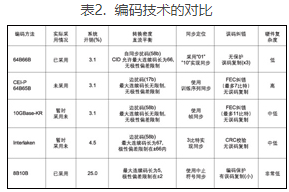

表2对比了以上讨论的几种编码技术的异同,主要包括以下几点:

实际采用情况;

系统开销;

转换密度与直流平衡;

同步定位;

误码(保护、校验、复制);

硬件复杂度(门数目)。

虽然8B10B编码行之有效,而且被广泛采用,但是它高达25%系统开销的缺点在未来数百吉比特链路与系统应用中显得越来越突出。现在已经有若干种低开销的编码技术,它们具备不同的优势与缺点。但是到目前为止,还没有哪种低开销技术能够脱颖而出,成为继8B10B之后被广泛采用的首选技术。不过,本文所提到的几种技术都以提高硬件复杂度为代价,以满足低开销的要求。

责任编辑:gt

关于接口,总线,驱动就介绍完了,您有什么想法可以联系小编。