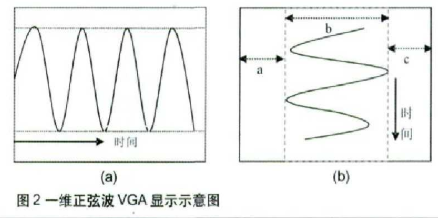

在具体实现时,需要对一维正弦波信号的参数作两点控制:控制正弦波的频率,保证一行扫描对应一个采样点;控制正弦波的幅度,将其控制在1024×768的有效显示区域中。

对正弦波频率来说,如果频率太高,一行会扫到多个采样点;如果频率太低,一整屏无法显示一个完整周期的信号。在本设计中,用一个较低的采样时钟控制正弦波的采样,正弦波存放在一个查找表中。如果要在一屏中显示n个周期的正弦信号,那么需要的采样频率fs=刷新率×n×查找表中一个周期的点数。

控制正弦波幅度即让正弦波的最大值不能超出屏幕的显示区。VGA有效显示宽度为1024,则屏幕两端的空闲部分宽度(图2(a)和(c))都为100。

二维图像信号的显示方式

二维图像的显示过程较一维信号容易实现。对二维图像,可以将二维图像信号转变成一维像素序列。在屏幕显示区域内,当行与场同步信号扫过时,将该像素点对应的RGB值进行赋值,就可以完成二维图像的显示。对于本设计,VGA时序为1024×768模式,图像的像素数在这个范围内可以完全在屏幕上显示,不会发生像素丢失。如果图像比较小,还可以将图像控制在屏幕的任意区域内。由于图像大小受存储空间限制,如果想要实现更高像素点的图像,就必须借用外部的SRAM或SDRAM来做图像缓存。

Avalon MM接口控制

在DSP Builder中,Altera提供了本设计与SOPC的接口——Avalon MM接口。

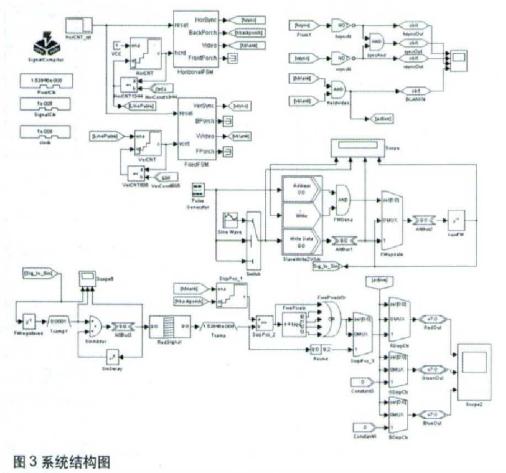

Avalon MM接口定义的接口信号主要有片选、读使能、写使能、地址,以及数据等。根据外设的逻辑,选用不同的接口定义信号,通过这些信号Avalon主端(CPU)可以向挂在Avalon总线上的从端外设写地址与数据信号,Avalon主端外设也可以主动去获取Avalon总线上的SRAM或SDRAM中的数据。不管是主传输还是从传输,都需要符合Avalon总线的读写时序才能发起一次正确的数据传输。可以利用Avalon MM接口将DSP Builder中设计的模块做成自定义外设。NiosⅡ CPU就可以利用Avalon总线与DSP Builder中产生的自定义外设进行通信,在本设计中对集成到SOPC系统上的VGA接口的地址赋值为0x1后,数据写入0x1,VGA接口控制器接收到数据,就会根据设计产生VGA时序信息及RGB信号,在屏幕上显示图像。图3为整个一维信号VGA显示系统的结构图。

仿真与硬件验证

本设计在2C70 DSP硬件开发平台下验证。