事实上,C模式能够满足绝大多数的应用需求,而且C模式的本地总线操作时序最简单,逻辑控制相对容易,其开发难度相对较低,因此,如无特殊需求,建议采用C模式。

2 、总线仲裁

在PCI9054与本地总线的接口设计中,一般需采用一片可编程逻辑器件CPLD/FPGA进行逻辑控制。在其控制逻辑中,总线仲裁逻辑是最关键、最核心的部分,直接影响计算机运行的稳定性。如果总线仲裁逻辑设计不合理,当计算机对PCI扩展板上的硬件资源进行访问时,计算机将会死机,因此PCI9054本地总线的所有控制逻辑必须服从于总线仲裁逻辑。

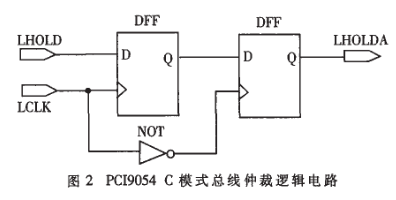

下面以C模式为例对PCI9054的总线仲裁逻辑进行探讨。在C模式下,PCI9054的143脚LHOLD和144脚LHOLDA是总线仲裁输入输出信号控制引脚,从公开发表的论文来看,有人将这两个引脚直接与设计电路相连进行总线仲裁逻辑设计。笔者在设计时也曾采用过这种方式,结果计算机运行很不稳定,经常莫名其妙地死机。仔细分析这种方式设计的电路会发现,该设计电路其实是利用器件的引脚传输延时配合总线仲裁电路的时序关系的。一般情况下,当环境温度、工作电压等外界因素变化时,大多数据逻辑器件的引脚延时会有相应的变化,因此用器件引脚延时设计出的总线仲裁逻辑电路运行不稳定应该是预料之中的事。

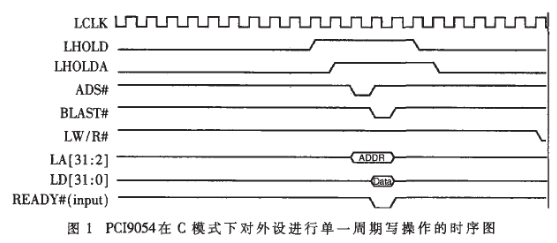

利用D触发器只在触发时钟有效边沿对信号敏感的特性进行设计,提高电路运行的稳定性,是可编程逻辑器件设计中的一种常用技巧。图1是PCI9054在C模式下对外设进行单一周期写操作的时序图,图2是利用可编程逻辑器件中的D触发器设计出的总线仲裁电路。

在图1中,ADS#、BLAST#和READY#信号的时序配合很重要,如果配合不好,计算机同样会死机。要提高电路稳定性,其设计思想与图2中的总线仲裁逻辑电路的设计思想相似。从多次实验情况来看,无论使用哪种工作模式,在该设计思想下设计出的本地总线控制逻辑电路运行非常稳定,没有死机的情况发生。

3、 存储器和I/O操作

通常PCI扩展板应该有配置空间、存储器空间和I/O空间三类资源。空间配置是必须的,根据设计需要,后两种资源可以只包含其中之一。PCI9054有S0和S1两个配置空间,两个配置空间都可以配置成存储器空间和I/O空间,存储器空间和I/O空间的配置既有相同之处,也有很大的区别。其相同点为两者都以字节为单位进行空间配置。不同之处有以下几点: