3.2信号处理模块

信号处理模块是系统的核心,由于成像算法的复杂性,选用AD公司的ADSP-TS201作为主处理器。这是一款极高性能的静态超标量处理器,他将非常宽的存储器宽度和双运算模块组合在一起。TigerSHARC静态超标量结构使DSP每周期执行多达4条指令、24个16位定点运算和6个浮点运算。运行在500 MHz时,TS201可提供48亿次40位的MAC运算或者12亿次的80位MAC运算。TS201的链路口时钟和数据线采用低压差分信号,可以达到很高的速度,单个链路口全双工工作的速度可以达到1 GB/s。TS201有丰富的内部存储资源,能提供33.6GB/s的内存带宽,特别适合并行组成高速并行处理器。从多片互连来看,他除了有完善的总线仲裁机制外还有4个高速链路口,可以以各种拓扑结构互连DSP,满足大运算量的要求。

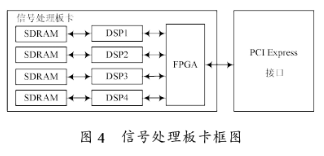

根据R-D算法既是并行的又是流水的特点,这里设计了分布式的并行系统。板卡拥有4片TS201,1 GB的存储空间。4个DSP采用分离总线的形式与一片FPGA相连,每个DSP都有独立的256 MB、64位宽度的SDRAM,4个DSP可以同时访问自己的SDRAM。系统采用标准的PCI Express总线。板卡上的FPGA负责整个板子的控制和接口工作。内核工作在500 MHz时,板卡的峰值运算能力达到每秒120亿次浮点运算。图4为信号处理板卡的框图。

4个DSP分布式互连,可以通过链路口进行数据交换,也可以通过FPGA进行数据传输。链路口是全双工的,可以稳定工作在500 MHz的时钟频率下。每个DSP的64位数据总线连到FPGA,在FPGA中设计了交换电路,任意两个DSP之间的数据交换速度为800 MB/s。DSP之间的链路口两两互连。

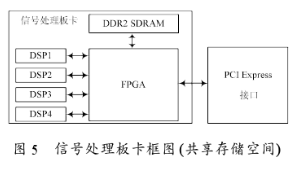

另外我们也设计了共享存储空间的信号处理板卡,存储器采用DDR2 SDRAM,由FPGA控制,容量为2 GB,时钟266 MHz,由于采用双倍数据率,单个数据线传输速率最高可达533 Mb/s,64位数据线的传输率最高4 200 MB/s。各个DSP总线都连接到FPGA上,DSP的外部时钟为100 MHz,64位总线的数据传输率可达800 MB/s,4个DSP同时访问时速度为3 200 MB/s。DSP通过FPGA来访问存储空间,当多个DSP同时访问时,在FPGA内部控制访问顺序。4个DSP的链路口仍是两两互连,结构如图5所示。

我们根据R-D算法的特点利用多处理器并行结构设计了体积小、功耗低、效率高的信号处理机。采用子孔径方法进行距离向处理,在第一个子孔径完成距离向处理后就可以开始数据转置,所以距离向处理可以按子孔径来进行流水处理,数据转置可以与之同时进行。为了实现整体的流水作业,距离向处理和方位向处理应该在不同的运算模块中进行,这样在对前幅图像进行方位向处理时,可以对下幅图像进行距离压缩和数据转置。