今天小编要和大家分享的是接口,总线,驱动相关信息,接下来我将从基于DPI-C接口的UVM验证平台设计与实现介绍,trekuvm这几个方面来介绍。

接口,总线,驱动相关技术文章基于DPI-C接口的UVM验证平台设计与实现介绍

0 引言

近几十年来,集成电路事业发展迅速,设计与工艺技术不断发展,更多和更复杂的功能被集成到一块芯片上。SoC的集成度和复杂度大大提高,在IC设计中就容易引入错误,所以验证工作将变得艰巨。随着IC设计规模的增大以及设计周期的压缩,传统验证技术已经不能再满足日益增长的验证需求,验证方法学应运而生,目前,UVM验证方法学已经成为应用最广泛的方法学。

本文目的在于为数字基带处理单元中标签发送链路的编码模块搭建一个适当的、完善的验证平台,用来验证RTL代码的正确与否。运用面向对象思想的UVM验证方法学和C语言进行平台的设计与实现,它能有效地缩短验证周期,提高验证效率,加大芯片的面试可能性。

1 UVM验证方法学

目前,主流的验证方法学有VMM、OVM和UVM。UVM基于System Verilog语言,具有VMM、OVM等诸多验证方法学的优点,是一套高效、开源的验证方法学。UVM由Accellera标准组织推出,并得到了三大主流EDA供应商支持。

通用验证方法学(Universal Verification Methodology,UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境。

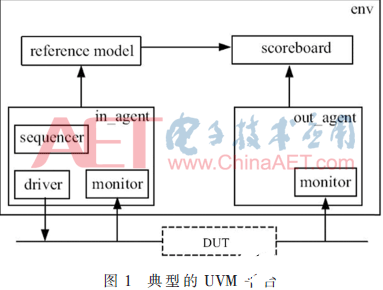

UVM平台架构主要是由通用验证组件(Universal Verification Component,UVC)构成。每个UVC都是功能完备、可配置、封装好的验证环境。根据UVC功能的不同,可分为接口UVC(Interface UVC)和模块UVC(Module UVC)等。

由图1可知构成UVM环境的常见组件类如下:

(1)uvm_driver类:是从uvm_sequencer中获取事务(transaction),经过转化在接口中对DUT进行时序激励。diver类与sequencer类之间的通信就是为了获取新的事务对象,这一操作通过pull方式实现:

driver.seq_item_port.connect(sequencer.seq_item_export);

driver.rsp_port.connect(sequencer.rsp_export);

(2)uvm_monitor类:用来监测数据。

(3)uvm_sequencer类:就像一个管道,从中传送连续的激励事务,并最终通过TLM端口送至driver一侧。