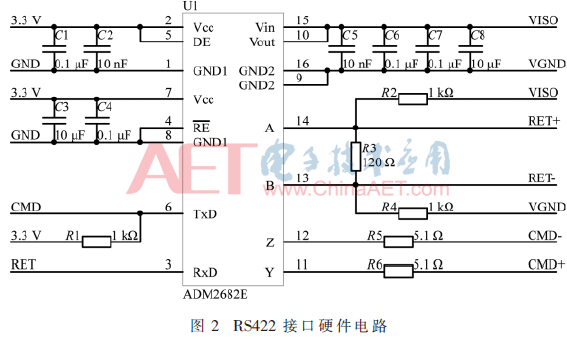

该接口电路选用ADI公司的磁隔离全双工收发器ADM2682E,无需外接DC/DC隔离模块。但是输入输出的供电引脚需要电源旁路,噪声抑制需要一个低电感高频电容,纹波抑制需要一个大容量电容。为了抑制噪声和降低纹波,至少需要并联两个电容,其中容值较小的电容靠近器件摆放。因此,在器件的VCC与GND1,VISOIN、VISOOUT与GND2之间均要加去耦电容。

差分输入端R2将差分输入正端上拉至VISO,R4将差分输入负端接地,这样做的好处是可以防止因为差分信号长距离传输造成的信号削弱,阻值均选择1 kΩ;因为数据传输电缆为特性阻抗为100 Ω的第五类屏蔽双绞线,R3的作用是可以减少信号的反射和衰减,提高数据传输的可靠性,阻值选为120 Ω。

3 LVDS接口设计

3.1 硬件接口

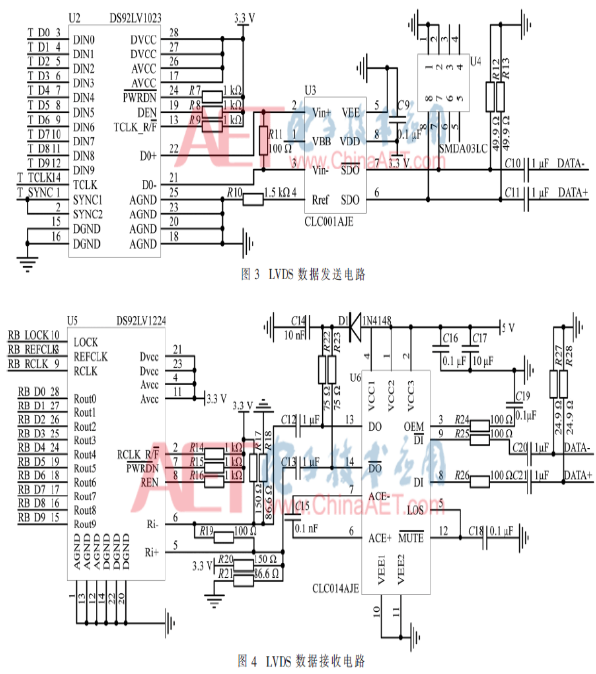

LVDS技术采用低压摆幅和和低电流驱动输出,具有很强的抗干扰性[2-4]。TI公司的DS92LV1023和DS92LV1224分别是高速串行差分数据流串化器和解串器。

在系统上电后,DS92LV1023和DS92LV1224将所有输出引脚置为三态后,启动锁相环跟踪并锁定本地的全局时钟。LVDS串化器连续给数据接收端的解串器发送同步信号,当解串器锁相环成功锁定同步时钟后,LVDS接口将串行数据送出。同理,LVDS解串器也需要与发送端同步后才能接收数据。若在数据传输的过程中解串器锁相环失锁,时钟紊乱,则LOCK信号会置高电平以通知串化器进行再同步的操作。

为了延长LVDS数据的传输距离,在发送端和接收端分别增加了电缆驱动器和电缆均衡器,以此来增强差分信号的驱动和补偿能力。驱动器CLC001AJE的传输速率最高可达622 Mb/s,通过配置外围电阻将DS92LV1023输出的低压差分信号压差从200 mV提升至0.9 V~1.1 V,有效增强了信号的驱动能力。在信号的接收端,信号经过屏蔽双绞线传输,衰减后很容易造成码间串扰,均衡器CLC014AJE可针对带宽50 Mb/s~650 Mb/s的信号进行补偿。恢复信号强度后,再通过DS92LV1224将串行数据解串[5]。LVDS数据发送、数据接收电路分别如图3、图4所示。

3.2 软件逻辑设计

LVDS逻辑控制示意图如图5所示,控制模块由FPGA内部的FIFO完成数据的缓存。上电后,LVDS发送模块向外部发送同步信号Sync,FIFO空标志信号Prog_empty为0时,FIFO读使能信号FIFO_rden_reg置1,将FIFO中的数据读出,然后向外部接口发送,线上空闲时发送无效数据[6-7]。