系统上电复位后状态机在S0状态循环等待。当上位机下发指令时,CPCI总线将Lhold信号拉高来申请本地总线,本地总线将Lholda信号拉高作为应答信号将总线控制权交给PCI9054。然后CPCI总线将Ads#拉低,开启新的总线传输,将命令字写入约定好的地址LA0。FPGA在检测到Ads#有效后离开S0进入S1状态。判断Blast#为低,进入单周期传输模式,判断LW/R#为低,执行Target读操作,即从CPCI总线接收上位机下发的命令字,然后拉高Ready#和Blast#表示单周期读操作结束。接着状态机返回S0继续检测Ads#信号。根据协议,FPGA会接着执行一次单周期Target写操作,将收到的命令字向上位机返回,由上位机对比两次命令字,结果一致表明命令下发成功,否则重新发送。这种增加反馈确认程序的命令下发模式有效保证了命令发送的准确性。

当下发的命令字要求上传数据时,FPGA将内部FIFO缓存的半满标志根据协议写入固定地址,上位机每间隔一定个CLK会自动执行一次单周期读操作,读取该地址的标示内容,若标示有效,则状态机进入DMA突发传输模式时,结束后返回S0状态,继续读取半满标示,直到命令结束。

这种结合PCI Target单周期模式读写指令和DMA突发模式传输数据的传输模式,既在节省CPU资源的同时保证了命令的准确下发和反馈,也有效发挥了CPCI总线的高速传输数据的优势[10]。

5 仿真与试验结果分析

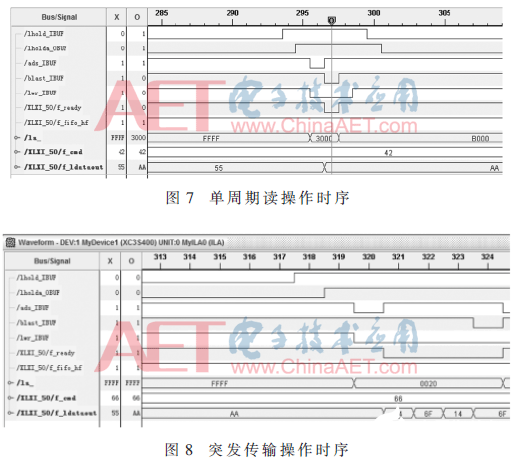

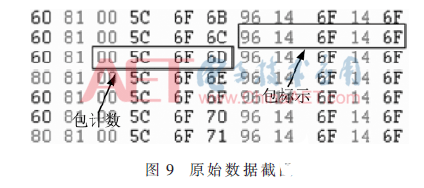

调试使用ISE配套的ChipScope Pro软件实时分析本地总线操作时序,图7为单周期读操作时序。在上位机下发上传数据的指令42H后,CPCI总线每400个CLK自动执行一次单周期读操作,判断地址0x3000内的数据标示是否为AA,如果是,说明缓存已准备好有效数据,上位机可以突发取数。经过390个CLK后,上位机开始突发取数,图8为突发取数操作时序,上位机从地址0x0020~0x1820取走FPGA写入的2K数据,每次突发4 B。实际工作时序与CPCI本地接口的理论时序一致。图9是上位机解包后的原始数据,其中包标示用于区分模拟量和数字量,包计数用于鉴定丢包。整个数据文件帧结构完整,包计数连续,没有丢数现象,进一步证明了本设计中CPCI接口与本地接口衔接合理,方案可行。

6 结论

本设计以PCI9054和FPGA控制器为核心,以LVDS为数据传输接口,从软硬件两个方面介绍了CPCI总线和本地总线的交互设计,通过协议转换芯片简化了整个设计,完成了数据传输卡与上位机之间的通信。测试结果表明,本设计方案可行、可靠,同时也可以为PCI、PXI平台的设计提供参考价值。