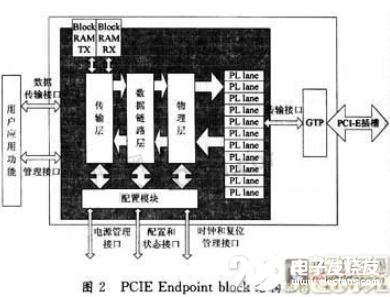

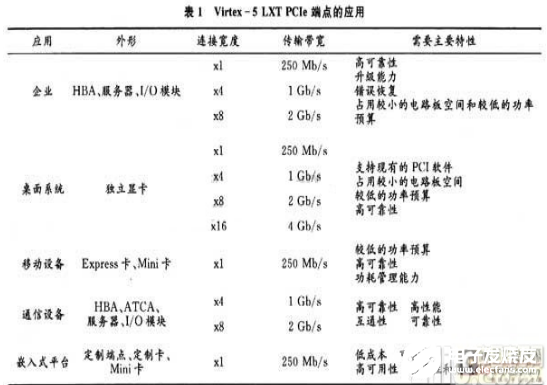

Virtex 5 Lxt PCIE Endpoint block具有PCI-Express的完整功能,完全符合PCIe基本规格v1.1版要求,作为FPGA内部的硬核,它是可配置的PCIe端点解决方案,大大增加设计的灵活性,降低设计的RNE费用,并且支持1x,2x,4x或8x通道的实现,为系统的功能扩张提供了有效途径;带有内置PCIe端点模块的Virtex-5 LXT FPGA芯片,能够被用于任何一种外形的产品设计,如表1所示。

3 总线接口设计实现

3.1 接口硬件设计

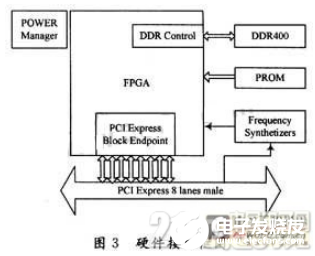

接口硬件主要由主控FPGA模块,电源管理模块,DDR高速缓存模块、和时钟管理模块组成。硬件结构框图如图3所示。

FPGA是整个设计的最关键部分,主要实现:PCI-Express硬核;在硬核的用户接口和传输接口实现PCI-Express传输本地总线的时序逻辑;并且在其内部完成DDR控制时序逻辑。FPGA是PCI-Express接口和DDR内存单元数据传输的通道。这里选择XilinxVirtex5系列FPGA中的V5LX50T芯片,封装形式为FFGll36。

在整个电路中,FPGA的功耗最大,因此在电源模块设计中,重点考虑FPGA因素。FPGA的功耗与设计有关,主要取决于器件的型号、设计的时钟频率、内部设计触发器翻转率和整个FPGA的资源利用率。这里使用Xilinx功耗分析工具XPower进行功耗分析,根据XPower提供的动态功耗和静态功耗分析结果,选择TI公司的相关电源模块。

DDR是比较常用的高速缓存单元,这里选择使用现代公司的HY5DU56822DT-D4,在PCI-Express传输过程中,对时钟的稳定性要求很高;Virtex5 FPGA内部的CMT模块的时钟综合处理能力可能达不到预想的效果,这里使用专门的时钟管理单元提供时钟,选择的是ICS874003芯片,通过FPGA管脚控制其时钟综合的效果。

3.2 软件设计

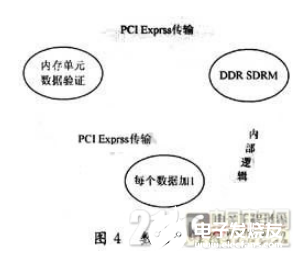

在实现PCI-Express数据传输过程中,构建数据传输流程如图4所示。

数据从PC内存通过PCI-Express接口向下传输到FPGA内部,FPGA内部DDR控制逻辑再将数据传输到的DDR内存芯片中存储,向下传输完毕后,FPGA内部逻辑从DDR芯片中将存储的数据读出,并且给每个数据按字节加‘1’,然后通过PCI-Express接口,再将数据传输回PC内存,PC内存程序对数据进行校验。