其中SCL为时钟输入端,数据随该时钟信号同步输入器件或从器件输出。此引脚上的输入缓冲器始终激活。SDA端为双向引脚,用于串行数据的输入输出;具有漏极开路,可与其它漏极开路或集电极开路输出进行线“或”;需上拉电阻,与SCL引脚配合,可实现400 kHz的2线I2C接口。VBack为备用电源输入端,用于VCC出现故障时向器件供电。是中断信号输出端,可通过设置报警寄存器按指定时间在该端产生报警信号;漏极开路,低电平有效。X1、X2分别为反相放大器的输入、输出端;可在X1端接入32.768 kHz的方波基准,或在X1、X2端接入32.768 kHz的石英晶振,配置成片内振荡器,在初始上电后至少有一个字节写入RTC寄存器时,时钟才开始计数。

X1203中的时钟/控制寄存器(CCR)分5部分:2个8字节报警寄存器(Alarm0、Alarm1),1个1字节控制寄存器,1个8字节实时时钟寄存器和1个1字节状态寄存器。通过报警寄存器可设置报警发生的时间,控制寄存器可使能或禁止报警中断信号的输出,实时时钟寄存器以BCD码存储了秒、分、时、日、星期、月和年,状态寄存器中保存了用于报警状态标志位及读写使能状态位。其中状态寄存器设置决定着数据是否能成功地写入。该寄存器如表1所列。

BAT标识器件当前用VBack还是用VCC工作。AL1、AL0标识Alarm0、Alarm1是否实时时钟匹配。RTCF表示实时时钟是否失效,在总电源失效后该位置1。RWEL为寄存器写使能锁存,为0表示禁止,在任何写时钟/控制寄存器之前必须将该位置1。WEL为写使能锁存,低表示禁止,通过该位写1、其它位写0,可使该位置位;通过该位写0、其它位写0,可使该位清0。只有按规定顺序设置RWEL和WEL,才能成功写入CCR。

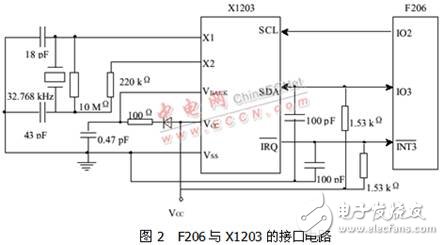

目前,很多DSP芯片尚不直接支持I2C的接口,F206也不例外,因而这里采用2根通用I/O口线模拟I2C接口。F206与X1203的接口采用如图2所示的接口方案。

图2中在X1、X2端接入32.768 kHz的石英晶振,将时钟源配置为片内振荡器。在VCC和VBACK之间通过二极管和电阻相连,并与地间加入1个0.47 F的大电容。这样,在电源出现故障或系统电源关闭时,仍可靠VBACK端的大电容供电维持时钟芯片的正常工作。它与F206间接口采用3根口线,这里采用IO2模拟通信用的时钟信号,IO3作为数据输入、输出口线。端可根据用户需要而定,若需要时钟芯片产生中断,可将该端接到F206的中断口线上。注意其中的SDA端和端为漏极开路,必须加上拉电阻,否则不能正常通信。

3.2 X1203的读写操作