2.2 模拟接口

模拟接口包括线输入、线输出和耳机输出。耳机输出可以驱动16Ω或32 Ω的耳机,音量增益为6 dB到一73 dB。

LLINEIN、RLINEIN:左、右声道输入。

LOUT、ROUT:左、右声道输出。

LHPOUT、RHPOUT:左、右声道耳机输出

2.3 数字音频接口

数字音频接口用于输入TLV320DAC23的D/A数据。

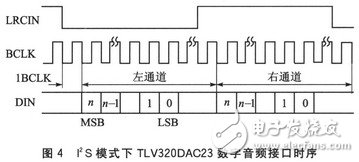

BCLK:I2S串行比特时钟。主模式时BCLK为输出,从模式时BCLK为输入。

DIN:I2S串行数据输入。

LRCIN:字时钟信号(帧信号),用于控制左、右声道的数据。在主模式中,由TLV320DAC23产生该信号,在从模式中,由主设备(如DSP或MCU)产生该信号。

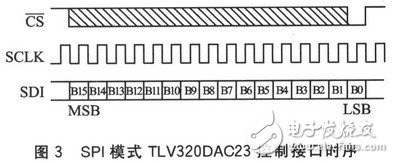

TLV320DAC23支持4种音频接口模式:右对齐模式、左对齐模式、I2S模式和DSP模式。这4种模式都是最高有效位MSB在前,16到32位不同的字长(右对齐除外,它不支持32位)。图4是I2S模式下的数字音频接口时序,数据的MSB在LRCIN下降沿后的第2个BCLK上升沿开始传输。

2.4 时钟接口

MCLK:芯片主时钟信号。当TLV320DAC23作为主设备时,该信号由芯片自身产生;当TLV320DAC23作为从设备时,该信号由外部产生。

CLKOUT:时钟输出信号。可以为MCLK或MCLK/2。

3 基于MCF5329的音频驱动设计

3.1 硬件电路

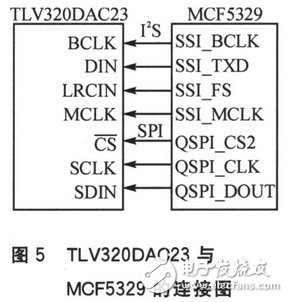

TLV320DAC23与MCF5329的接口有两个:一个是控制接口,用于设置TLV320DAC23的寄存器,从而设置它的工作参数。由于MCF5329具有QSPI模块,它兼容SPI接口格式,所以TLV320DAC23的控制接口采用SPI模式。另一个是数字音频接口,用于传输TLV320DAC23的音频数据并控制数据的时序。

在本设计中,由微控制器MCF5329提供时钟信号,所以将MCF5329设为主设备,TLV320DAC23作为从设备。具体连接如图5所示。

3.2 软件设计

音频播放的过程如下:程序检测到用户空间有需要播放的音频数据,便将音频数据拷贝到所建立的缓冲区中;然后通过DMA将缓冲区的音频数据传输到SSI模块的发送引脚SSI_TXD,发送引脚将数据发送至TLV320DAC23中,通过耳机播放出来。

软件设计的流程如图6所示。其中,音频缓冲区被设置为一个固定大小的循环队列,其设置如图7所示。初始时,bufstart、audiostart、audiotail都指向缓冲区头。当用户空间有数据时,将数据拷贝到缓冲区并用audiotail指示数据尾部,数据的头部通过DMA引擎连接到SSI_TXD引脚。