今天小编要和大家分享的是接口,总线,驱动相关信息,接下来我将从SoC芯片中内部总线模块的设计,marvell 88f5281是marvell专门为了nas这样的小型设备设计的soc这几个方面来介绍。

接口,总线,驱动相关技术文章SoC芯片中内部总线模块的设计

在芯片设计中,芯片内部总线的设计往往决定了芯片的性能、功耗与各模块设计的复杂度。我们设计总线往往会依据两方面的原则:一是芯片设计流程其内在的需求,二是所针对的应用对交换宽带、延时、效率、灵活性的需求。

针对芯片总线设计流程内在的需求,高效总线结构设计通常遵循的基本原则包括:同步设计、可综合、无三态信号、低延时、单触发延、支持多主控及总线仲裁(支持DMA及多CPU核)、高时钟频率独立性、支持突发(高效率)和低门数。遵循这些基本原则可以帮助我们规避很多设计上的风险,提高总线效率与IP复用度。当然,实际上述有些原则如“三态总线”,可以而且应当在某些应用中使用,只是不建议芯片及设计工程师轻易地突破这些规范,增加风险。南山之桥微电子公司在高端芯片设计中使用了三态总线技术来解决超宽总线的布线聚集与时序匹配问题。

应用的需求往往会决定总线的形式,如SoC芯片中往往会采用嵌入式CPU的总线结构。反过来说,我们选用哪一款CPU,除了成本、性能、功耗、快速精确的时序仿真模型、编译环境和可用IP外,还有重要的一点就是其总线设计是否简单、高效与有利于发挥其它设计模块的效率。

以现在较流行的ARM处理器来说,采用AMBA总线标准,其中高速芯片通常采用的AHB总线有以下几个特质:流水线式、非三态总线、支持多主控、总线仲裁与集中地址译码、应答响应机制(非实时)、支持突发。

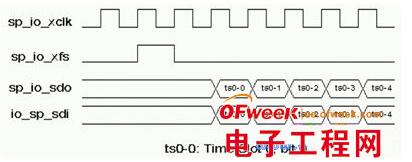

总之,AHB总线适宜于发挥CPU的效率,符合高效总线设计的原则,但是其本身也有总线位宽限制(主要是指令集位宽)与SPLIT(切分)选项支持的复杂度。在笔者参与的设计中有一半以上不支持SPLIT选项以降低设计与验证开销,限于篇幅在此不展开阐述。最主要的问题是SoC中CPU总线一般采用应答机制,也就是非实时的,数据的处理采用中断响应机制以发挥效率。处理特定实时数据并没有固定的延时与稳定的吞吐率,那么就需要设计一个模块来处理实时数据到非实时总线之间的平滑过度问题。笔者以此模块设计为例,阐述非实时总线中实时数据切换的设计理念与几个实用技术。例子中实时数据传递采用TDM总线形式(Time Division Multiplexed,时分复用),我们称此模式为TDM模块。