队列深度=最长AHB总线获得间隔×TDM输入速率

AHB总线轮询(poll)间隙取决于总线上有几个主控模式模块与仲裁的优先级策略。一般建议实时模块享有较高优先级,当然随之而来的要求是总线申请的频度不能太高。平衡这一对矛盾的解决办法超越本文论述的范畴,读者可以从“固定权重加优先级竞争”的仲裁机制入手来设计AHB总线仲裁器。

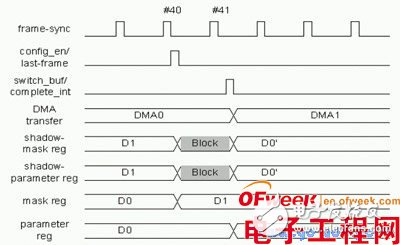

动态切换时机与影子寄存器的使用

在实际应用中,我们常常发现帧格式中很多时分信道并没有音频数据,这时就要采用时分掩码来屏蔽这些信道以阻止无效数据占用带宽。问题是时分信通中是否有数据是动态变化的,动态变化的数据要求时分掩码参数也要动态分配。但是怎么切换呢?这里采用“影子寄存器”技术,原理是两套寄存器,一套参数应用于当前帧,另一套应用于下一帧。利用帧同步头的一个时钟周期实时切换。而SoC中的CPU只看到一套寄存器地址,同时配置行为本身放宽了实时要求的限制,实时切换由TDM模块完成,具体图形见图4。

错误的处理--最后一根救命稻草

如大家深知,芯片设计是没有下一次机会的,那么错误的处理就成为了“救命的稻草”。假设TDM模块很久没有得到总线的控制,出现underrun(速率过低)与overrun(速率过高)情况。要采用队列中“high-watermark(高水线)”与“low-watermark(低水线)”技术,在队列接近满与空状态发生前提前预警。预警通常反映了芯片系统中的一些设计问题与当时电压波动、干扰、局部高温等瞬间问题,这时预警信号通常用最高/次高优先级中断发生。ARM CPU本身支持高优先级中断,而我们的队列长度计算现在要重新计算,加上高优先级处理这一段时间,具体的响应时钟周期,读者请查阅相应CPU手册,这也是评价嵌入式CPU与实时操作系统(RTOS)的一项指标。

队列深度=最长AHB总线获得间隔×TDM输入速率+ARM最长中断响应时间×TDM输入速率

本文小结

我们在TDM模块简要设计中,阐述了结合各种基本技术,如从缓存队列到DMA到影子寄存器到动态分配到watermark与利用DSP算法特性,AHB总线特性、帧同步特性以及RTOS特性解决非实时与实时交换、CPU效率与资源占用、延时与DMA配置与动态切换的矛盾,追求最优解决方案的过程与设计思路。

本文并没有给出最初方案的队列计算公式,是因为要考虑的因素过多,从另一个侧面反映了它不是最优方案。好的设计应该是把复杂的需求简单化、模块化,当然实际设计中比这种简化设计要复杂,例如还要解决实时数据传输中双方时钟不同步等问题。但读者只要掌握了基本思路与技术,理解应用特性、CPU特性及RTOS特性与算法,就可举一反三,做出最优的设计。