今天小编要和大家分享的是接口,总线,驱动相关信息,接下来我将从基于RGMII接口的88E1512搭建网络通信系统,cpld fpga 接口板 外设板 扩展板 通用型强这几个方面来介绍。

接口,总线,驱动相关技术文章基于RGMII接口的88E1512搭建网络通信系统

一、前言

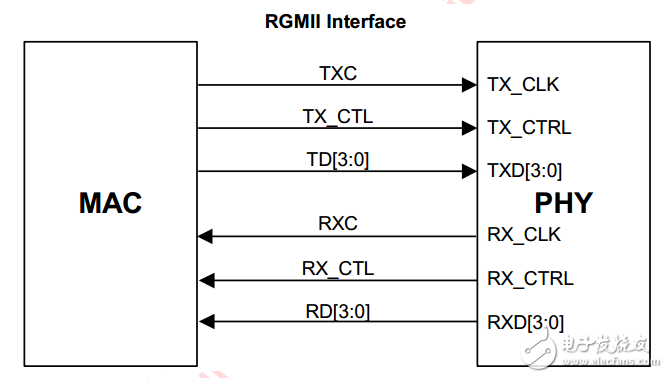

网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG。但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统。这类接口总线位宽小,可以降低电路成本,在实际项目中应用更广泛。

二、从GMII过度到RGMII

先看看GMII和RGMII主要的接口。

GMII:

发送 gmii_tx_clk gmii_tx_d[7:0] gmii_tx_en gmii_tx_er

接收 gmii_rx_clk gmii_rx_d[7:0] gmii_rx_dv gmii_rx_er

RGMII:

发送 tx_clk tx_d[3:0] tx_ctrl

接收 rx_clk rx_d[3:0] rx_ctrl

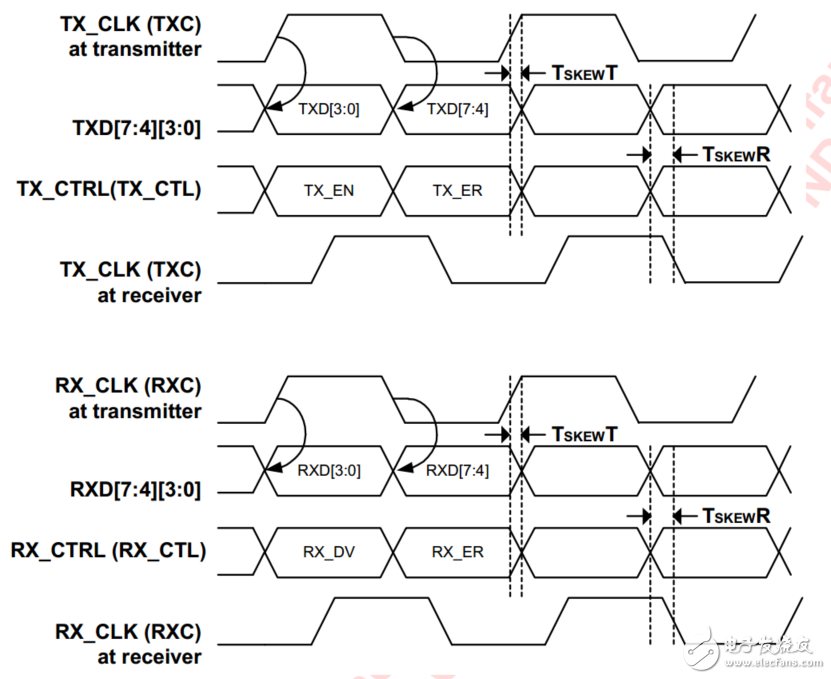

为什么接口变少了?首先数据总线从时钟单边沿采样8bit转变为了双边沿采样4bit,从88E1512 Datasheet中时序图可以直观看出这一点。

RGMII中上升沿发送一字节数据的低四位,下降沿发送剩余的高四位数据。接收端时钟双边沿采样,因此125MHZ*8bit = 125MHZ*4bit*2 = 1000Mbit/s。至于GMII中的数据有效和数据错误指示信号被ctrl信号复用:tx_ctrl在时钟tx_clk上升沿发送是tx_en,在下降沿发送是tx_en ^ tx_er。rx_ctrl在时钟rx_clk上升沿接收是rx_dv,在下降沿接收是rx_en ^ rx_er。综上,RGMII接口引脚数从25个降低到14个。

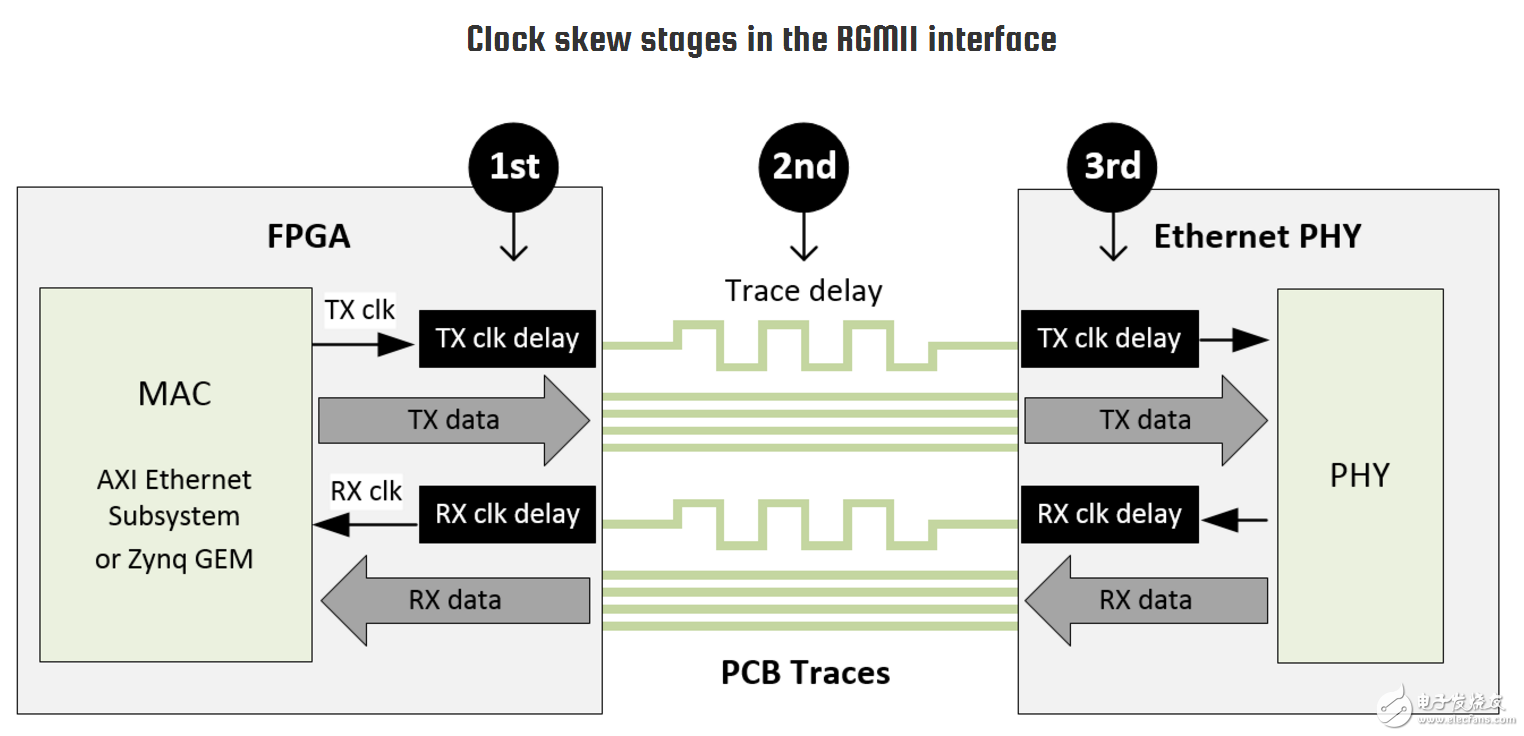

三、add clock skew

从上边的时序图分析,数据在时钟的边沿变化。因此如果不做额外处理,接收端无法稳定采样。为了解决这一问题,常见的做法是为时钟信号添加延时,使其边沿对准数据总线的稳定区间。可以在控制器端、PCB走线以及PHY芯片内部添加时钟偏移,本文使用最后一种方式实现。

在第三阶段中添加延迟。数据发送方向,FPGA侧的TX_CLK信号不需要额外处理,也就是说FPGA发送与数据边沿对齐的时钟信号。TXD和TX_CLK信号波形如图。