今天小编要和大家分享的是处理器,DSP相关信息,接下来我将从基于TMS3206713B和CycloneIII系列FPGA实现多路差分信号采集系统设计,fpga dsp这几个方面来介绍。

处理器,DSP相关技术文章基于TMS3206713B和CycloneIII系列FPGA实现多路差分信号采集系统设计

在信号处理过程中,经常采用DSP+FPGA协同处理的方法。是因为DSP虽然可以实现较高速率的信号采集,但其指令更适于实现算法而不是逻辑控制,其外部接口的通用性较差。而FPGA时钟频率高、内部延时小,全部控制逻辑由硬件完成,速度快、效率高,适合于大数据量的传输控制,可以集成外围控制、译码和接口电路,在高速数据采集方面有着DSP以及单片机无法比拟的优势,但缺点是难以实现一些复杂的算法。因此,若采用DSP+FPGA协同处理的方法,便可以使DSP的高速处理能力与FPGA的高速、复杂的组合逻辑和时序逻辑控制能力相结合,达到互补,使系统发挥最佳性能。

在目前的信号采集及测试系统中,由于应用背景的复杂,经常需要对多路信号进行采集,有的甚至需要对多路单端及差分信号进行采集,在某些情况下,为测试分析的方便,还需要对采样率进行改变。文中介绍了一种采用DSP+FPGA协同处理的方法,并主要利用ADS8517这一A/D转换芯片来实现多路可以选择单端或差分输入的信号采集系统的设计方法。

1 系统实现功能

该系统可以实现32个通道单端信号或16个通道差分信号的采集输入,由DSP控制输入信号是单端信号还是差分信号,以及各自使能输入的通道,其中单端信号最多使能输入32个通道,差分信号最多使能输入16个通道。A/D在各个使能通道间采用类似时分复用的方法进行轮寻采样,A/D采样频率200 kHz,DSP可设置采样率分频值,对采样率进行改变,假如DSP设置采样分频值为D,使能输入通道数为N,则每个通道实际采样率为200 kHZ/(D·N)。

2 系统硬件设计

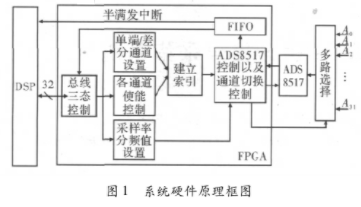

根据以上功能要求,整个系统的设计思路如图1所示。其中DSP采用TI公司的TMS3206713B,FPGA采用Altera公司的CycloneIII系列,A /D采用TI公司的ADS8517。ADS8517的主要性能:(1)16位分辨率;(2)采样频率:200 kHz;(3)模拟输入范围±10 V;(4)输出有串行和并行两种方式。