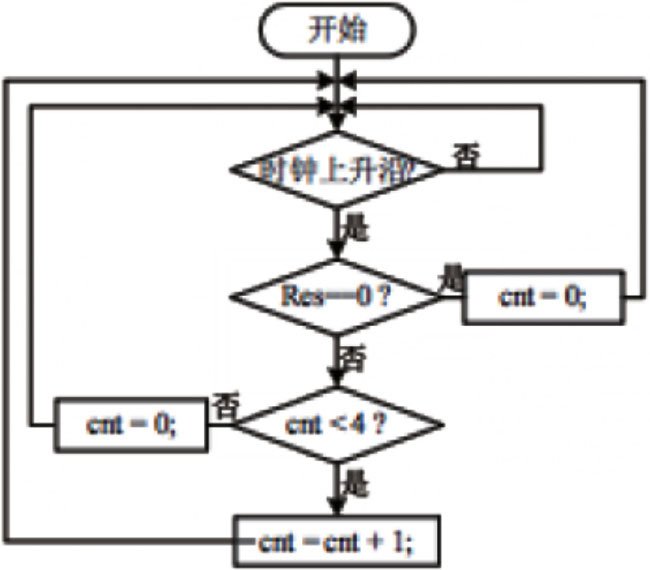

下面以设计一个五进制加法计数器为例来讨论 EDA 在数字逻辑电路实验中的具体应用。在此设计一个带有复位端的计数器, 端口分别为:clk(时钟,输入端,位宽为1),res(复位,输入端,位宽为1),cnt[2,0](计数端,输出端,位宽为3)。时钟 cl k 为上升沿触发,复位 r e s 低有效,计数端 cnt[2,0] 有效数据范围为3’b000~3’b100。程序流程图如图2 所示。

图2 五进制计数器流程图

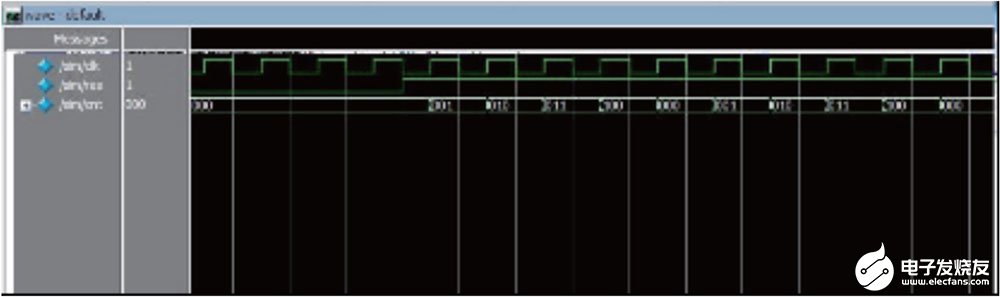

通过对五进制计数器的分析,用 VerilogHDL 描述出功能后, 在 Quartus II 11.0 软件上联合 Modelsim 进行仿真后,得到如图3 所示的仿真波形。

图3 五进制加法计数器仿真波形

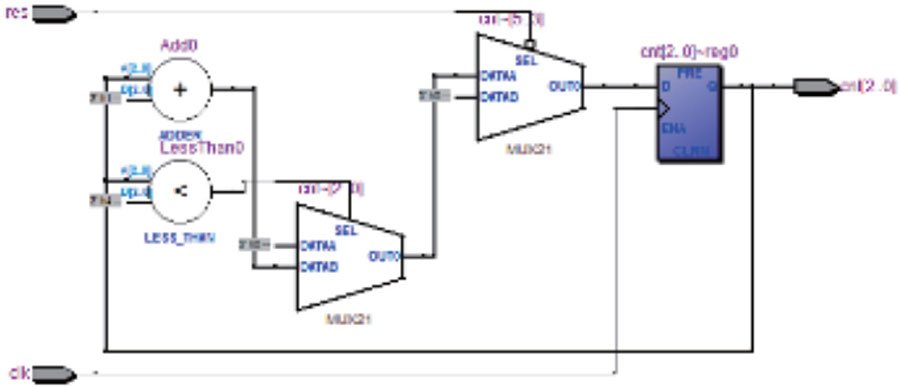

通过波形图我们可以看出,所设计的逻辑功能和设计要求完全一致,通过 QuartusII11.0 综合后的电路图如图4 所示,我们可以观察出五进制计数器有哪些基本的逻辑器件所组成,最后将设计的项目通过 Quartus II 11.0 软件下载 / 配置到相对应的实验箱, 学生可以很直观的观察到计数器的逻辑功能。

图4 五进制计数器综合电路图

我们必须熟悉各个逻辑器件以及要设计出的电路图的具体的组成,才能构造出总的电路图,而对于 EDA 技术我们只要了解了它的功能,根据它的功能用硬件语言描述出来,通过软件的综合后就可以得到对应的电路图。尤其是对于一些复杂的电路,利用 EDA 技术比传统的实验教学更简单方便, 更易掌握。

关于EDA,IC设计就介绍完了,您有什么想法可以联系小编。