许多类型的传感器会产生意想不到的、与它们要测量的物理现象无关的输出尖峰,这类过压状况一般仅影响输入引脚。

静电放电是一种广为人知的过压事件,常常发生在安装器件之前。它造成的损害非常广泛,以至于业界主要规范,如 JESD22-A114D 等,不得不明确如何测试和规定半导体耐受各类 ESD 事件的能力。几乎所有半导体产品都包含某种形式的集成保护器件。应用笔记 AN-397(标准线性集成电路的电诱发损坏:最常见起因和防止再发生的相关处理)是一篇很好的参考文献,详细讨论了这一问题。出现高能脉冲时,ESD 单元应进入低阻抗状态。这不会限制输入电流,但能提供到供电轨的低阻抗路径。

一个简单的案例研究:电源时序控制

随着混合信号电路变得无处不在,单一 PCB 上的多电源需求也变得非常普遍。关于新设计需要考虑的一些微妙问题,特别是需要许多不相关的电源时,请参阅应用笔记 AN-932(电源时序控制)。

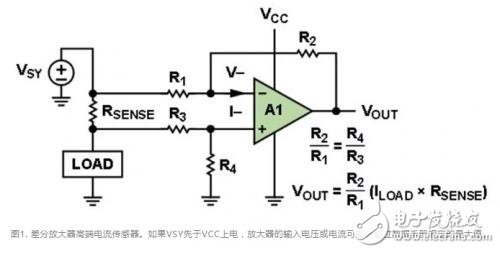

精密放大器可能会成为这种状况的受害者。图 1 显示了一个配置成差分放大器的运算放大器。放大器通过 RSENSE 检测电流,并提供与相应压降成比例的输出。必须采取措施,确保由 R3 和 R4 构成的分压器将输入偏置在额定 IVR 范围内的某处。如果放大器的电源电压不是从 VSY 获得,并且 VCC 在 VSY 之后出现,则 A1 反相输入端的电压为:

其中 I–由无电源时 A1 的输入阻抗决定。如果放大器不包含过压处理设计,则最有可能的电流路径是通过 ESD 二极管、箝位二极管或寄生二极管流向电源或地。如果此电压超出 IVR 范围,或者电流超过数据手册规定的额定最大值,器件可能会受损。

ADA4091 和 ADA4096 等过压保护放大器所用的 ESD 结构不是二极管,而是 DIAC 器件(双向“交流二极管”),这使得此类放大器即使没有电源也能承受过压状况。

运算放大器中的故障状况

图 2 显示了一个 N 沟道 JFET 输入级(J1、J2、R1 和 R2),后接一个第二增益级和输出缓冲器(A1)。当开环放大器在其额定 IVR 范围内时,差分输入信号(VIN+ – VIN–)与 VDIFF 180 度异相。连接为单位增益缓冲器时(如图所示),如果 VIN+的共模电压超过放大器的 IVR,J1 的栅极 - 漏极进入未夹断状态并传导整个 200 μA 级电流。只要 J1 的栅极 - 漏极电压仍然反向偏置,VIN+的进一步增加就不会导致 VDIFF 变化(VOUT 仍然处于正供电轨)。然而,一旦 J1 的栅极 - 漏极变为正偏,VIN+的进一步增加就会提高 A1 反相输入端的电压,导致输入信号与 VDIFF 之间发生不需要的反相。