8. 一般小电路组=》无特殊要求;走线平顺。

9. pull height R、RP =》无特殊要求;走线平顺。

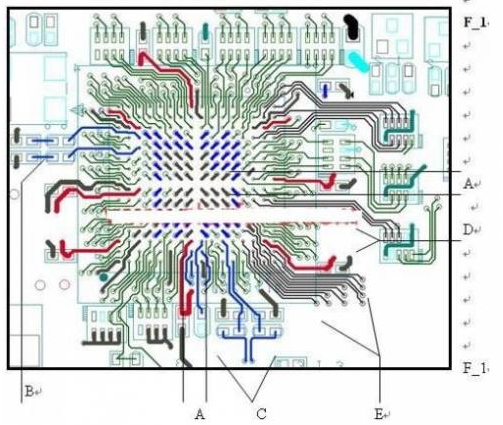

为了更清楚的说明 BGA 零件走线的处理,将以一系列图标说明如下:

A. 将 BGA 由中心以十字划分,VIA 分别朝左上、左下、右上、右下方向打;十字可因走线需要做不对称调整。

B. clock 信号有线宽、线距要求,当其 R、C 电路与 CHIP 同一面时请尽量以上图方式处理。

C. USB 信号在 R、C 两端请完全并行走线。

D. by pass 尽量由 CHIP pin 接至 by pass 再进入 plane. 无法接到的 by pass 请就近下 plane. E. BGA 组件的信号,外三圈往外拉,并保持原设定线宽、线距;VIA 可在零件实体及 3MM placement 禁置区间调整走线顺序,如果走线没有层面要求,则可以延长而不做限制。内圈往内拉或 VIA 打在 PIN 与 PIN 正中间。另外,BGA 的四个角落请尽量以表面层拉出,以减少角落的 VIA 数。

F. BGA 组件的信号,尽量以辐射型态向外拉出;避免在内部回转。

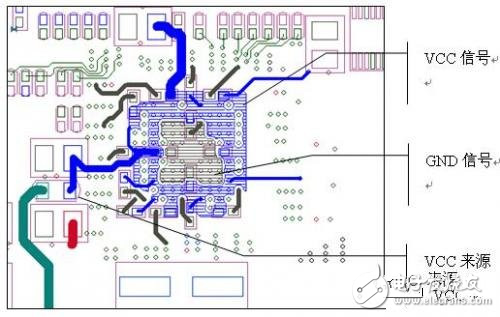

F_2 为 BGA 背面 by pass 的放置及走线处理。

By pass 尽量靠近电源 pin. F_3 为 BGA 区的 VIA 在 VCC 层所造成的状况 THERMAL VCC 信号在 VCC 层的导通状态。

ANTI GND 信号在 VCC 层的隔开状态。

因 BGA 的信号有规则性的引线、打 VIA,使得电源的导通较充足。

F_4 为 BGA 区的 VIA 在 GND 层所造成的状况 THERMAL GND 信号在 GND 层的导通状态。

ANTI VCC 信号在 GND 层的隔开状态。

因 BGA 的信号有规则性的引线、打 VIA,使得接地的导通较充足。

BGA 芯片的布局和布线设计方法解析

F_5 为 BGA 区的 Placement 及走线建议图

以上所做的 BGA 走线建议,其作用在于:

1. 有规则的引线有益于特殊信号的处理,使得除表层外,其余走线层皆可以所要求的线宽、线距完成。

2. BGA 内部的 VCC、GND 会因此而有较佳的导通性。

3. BGA 中心的十字划分线可用于;当 BGA 内部电源一种以上且不易于 VCC 层切割时,可于走线层处理(40~80MIL),至电源供应端。或 BGA 本身的 CLOCK、或其它有较大线宽、线距信号顺向走线。

4. 良好的 BGA 走线及 placement,可使 BGA 自身信号的干扰降至最低。

来源:互联网

关于EDA,IC设计就介绍完了,您有什么想法可以联系小编。