图4

再来看一个DDR3设计案例,某设计人员在数据信号中加入了串阻,拓扑结构如下图5:

图5

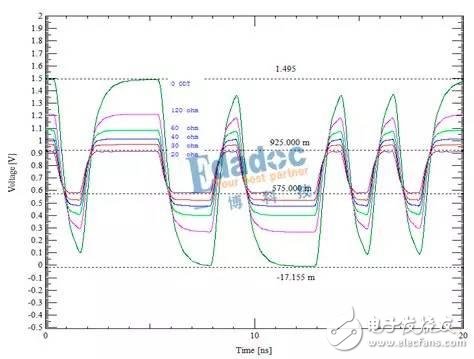

DDR3颗粒端有ODT功能,且有6种阻值可选,作者扫面这几种模式得到的波形如图6:

图6

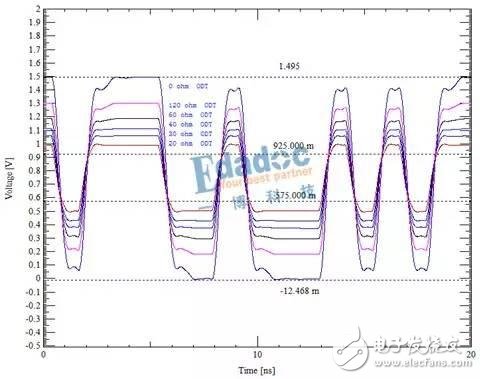

图6的波形,在开ODT的情况下波形裕量较小,DDR3本身带有ODT功能啊,为什么还要加串阻呢?于是我果断把串阻去掉,仿真波形如图7

图7

去掉串阻之后,波形的裕量更大了,且上升沿没那么缓了。所以,对于有ODT功能的DDR颗粒,布线时不用加串阻,这样不仅节省了元件,也节省了布线空间。

看来SI工程师是十分重要的哈,高速设计的成功离不开SI工程师的努力。拓扑结构的设计不是一劳永逸的,什么驱动芯片适合什么样的拓扑结构,需要仿真评估。仿真是一个不断尝试与探索的过程,它帮助我们找到互连与器件的最佳匹配。

来源:pcbbbs

关于EDA,IC设计就介绍完了,您有什么想法可以联系小编。