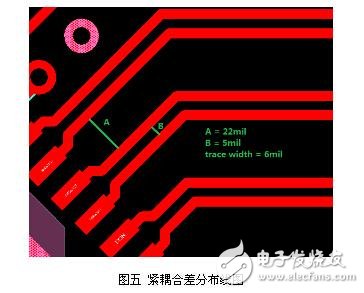

图五是针对上述设计使用紧耦合差分线进行串扰优化的一个实例:

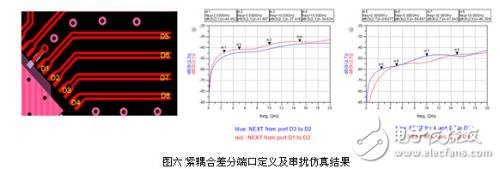

图六是上述设计的差分模式的近端串扰和远端串扰的仿真结果:

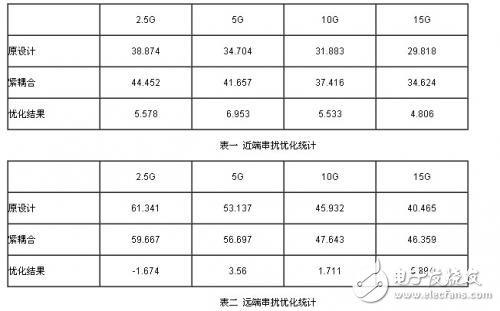

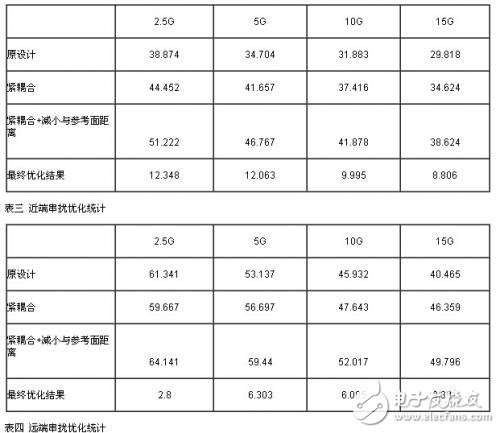

从优化后的仿真结果可以看出,使用紧耦合并增加差分对之间的间距可以使差分对间的近端串扰在0~20G的频率范围内减小4.8~6.95dB.远端串扰在5G~20G的频率范围内减小约1.7~5.9dB.

除了在布线时拉开差分对之间的间距并减小并行距离之外,我们还可以调整差分线走线层和参考平面的距离来抑制串扰。距离参考层越近,越有利于抑制串扰。在采用紧耦合走线方式的基础上,我们将TOP层与其参考层之间的距离由7mil调整到4mil.

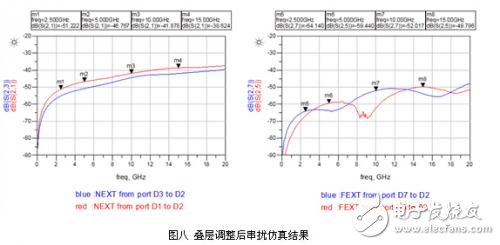

根据上述优化进行仿真,仿真结果如下图:

值得注意的是,当我们调整了走线与参考平面的距离之后,差分线的阻抗也随之发生变化,需要调整差分走线满足目标阻抗的要求。芯片的SMT焊盘距离参考平面距离变小之后阻抗也会变低,需要在SMT焊盘的参考平面上进行挖空处理来优化SMT焊盘的阻抗。具体挖空的尺寸需要根据叠层情况进行仿真来确定。

从仿真结果可以看出,调整走线与参考平面的距离后,使用紧耦合并增加差分对之间的间距可以使差分对间的近端串扰在0~20G的频率范围内减小8.8~12.3dB.远端串扰在0~20G范围内减小了2.8~9.3dB.

四、结论

通过仿真优化我们可以将由小间距QFN封装在PCB上引起的近端差分串扰减小8~12dB,远端串扰减小3~9dB,为高速数据传输通道提供更多裕量。本文涉及的串扰抑制方法可以在制定PCB布线规则和叠层时综合考虑,在PCB设计初期避免由小间距QFN封装带来的串扰风险。