外部信道

对于外部信道来说最常见的问题是,在两个不同的ADC中同时转换来自于一个焊盘的相同的模拟数据。造成这种情况的原因是,这两个ADC的采样电容器之间存在电荷共享。发生同时采样时,一个ADC的采样电容器上的保持采样电压会受到另一个ADC采样相位的干扰。这是因为应该为一个电容器充电的模拟电压遇到两个需要充电的电容器。由于电荷共享导致采样电容器采样的数值小于输入,从而导致ADC转换了错误的值。

可以保持软件限制以确保不会同时对共享的信道进行采样,从而解决这个问题。另一种解决方案是,如果发生了同时采样,则为第一个ADC提供较大的采样时间。这将允许第一个ADC重新设置它需要转换的电压,从而减少转换错误值的机会。

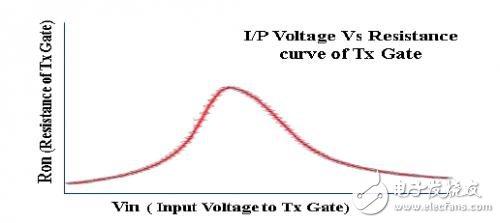

当这些内部/外部信道的路径中存在传输门时,会出现一个常见问题。传输门的电阻取决于输入电压,因此,如果一个动态信号(该信号的值随着时间不断变化)通过该路径到达ADC进行转换,则会出现SNR劣化。这是因为,随着传输门上模拟输入的值不断变化,其电阻也发生变化,导致采样时间也发生了改变。这样,采样数据不准确的几率就更大。解决这个问题的方法是,采用一个改良后的传输(Tx)门,它在整个输入范围内均可保持相当恒定的导通电阻。传输门的导通电阻与采样电容C间应有一个至少为10,000的因子,才能使THD小于80db

图4:传输门的RON与输入电压变化

图字:Ron(传输门电阻);I/P电压对传输门的电阻曲线;Vin(传输门的输入电压)

不同SoC操作模式下的ADC的时钟源

SoC以不同的模式工作。这些模式以芯片的不同活跃等级(电流消耗)区分。SoC可能拥有低功耗模式(部分活动模式)以及主运行模式(完全活动模式)。低活动或部分活动模式是指设备为了降低功耗以较低频率运行,时钟源通常是内部RC振荡器。在这些低功耗模式下,PLL通常被禁用。PLL是抖动非常低的时钟源,而RC振荡器则是抖动最大的时钟源。

让我们了解一下时钟源的抖动对SNR值的影响。采样周期和采样开始与结束时间以及转换与ADC工作的时钟源保持同步。为了让采样以相同的时间间隔进行,该时钟的沿本身应一致统一。任何有抖动的时钟都会产生不均匀的时钟沿,导致采样不一致。对于某些设计类型的ADC (SAR)来说,输入数据采样可能只在采样周期内在一个时钟沿进行,而对于其它类型(如Σ-Δ[SD] ADC)来说,采样可能在采样周期内在每个沿进行。因此,由于时钟抖动,SD ADC更容易出现SNR劣化。