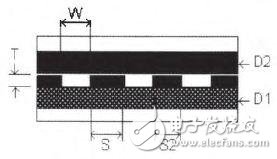

图4走线剖面图

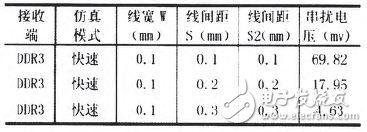

表1串扰分析结果

从表1可看出间距越大串扰影响越小,这里我们遵循的3W原则即走线边沿间距S是线宽W的3倍将大大减少串扰的影响。但间距增大将牺牲布线空间,因此需综合考虑使在有限的空间中布线最优化。

3.3时序分析

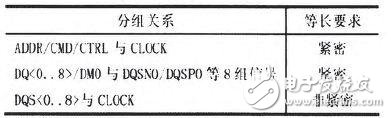

DDR3是并行总线,其时序属源同步系统,在满足信号质量的前提下,也必须满足时序要求。对于源同步时钟,驱动芯片的数据和时钟信号由内部电路提供即数据和时钟并行传输。DDR3对不同的时序关系采用分组设计,其时序关系如表2.

表2时序分组关系

源同步时序计算公式:

Tsetup_margin=Tvb—Tsetup—Tskew

Thold_margin=Tva—Thold—Tskew

公式中:Tsetup margin\Thold_margin:建立时间余量\保持时间余量,Tvb\Tva:驱动端的建立时间和保持时间,Tsetup\Thold接收端的建立时间和保持时间,Tskew:指数据、地址信号参考时钟引起的偏移。其中Tvb\Tva,Tsetup\Th01d参数值都是能从器件手册中获取,关键是数据与选通信号飞行时间的时序偏移(skew),包含驱动端输出的偏移和在PCB板上的走线长度的偏移,需通过时序仿真非理想随机码进行分析计算得出。

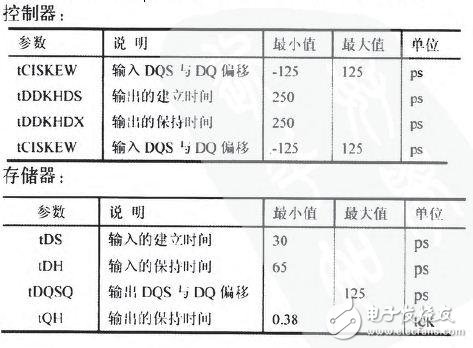

以DDR3数据读写操作为例,根据下表芯片资料中的时序参数进行静态时序裕量的计算,获得PCB设计的时序控制规则。

表3仿真所需要的时序参数(数据率:1333MHz)控制器:

写操作:

Tsetup_margin=0.25—0.03=0.22ns

Thold_margin=0.25-0.065=0.185ns

读操作:

Tsetup_margin = Thold_margin=(0.38*1.5-0.125)/2 - 0.125=97.5ps

上述计算值是理论上的时序余量,其实源同步时序除本身芯片自身固有特性所带来的延时外还受其他因素的影响,都属于偏移范围,主要包括:

(1)高速总线造成的信号完整性问题如串扰、同步开关噪声、码间干扰(ISI)等影响,需通过信号仿真分析来估算。

(2)高速总线互连所产生的时序偏斜:主要是信号总线互连链路中的布线误差,整个链路含器件封装内部走线、pcb板上走线和走线过孔等产生的时序偏差,可通过等长布线来控制其时序偏斜。