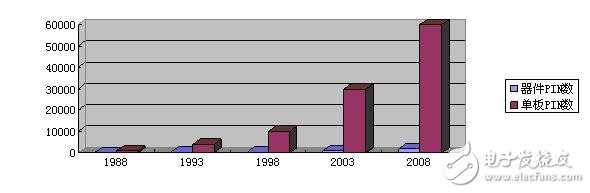

图3:单个器件PIN数目以及单块单板PIN总数的变迁

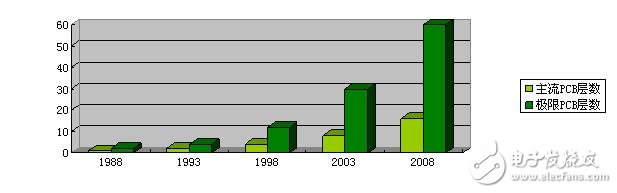

过去20年IT行业单板层数的变迁:

图4:单板层数的变迁

过去20年单板PIN密度(Pin density, Pins/sq in):的变迁:

图5:单板PIN密度的变迁

上述的数据里面我们能深刻的感受到PCB设计密度越来越高的压力,从20年前的跳线满板飞,发展到后来的双面板、多层板,再到器件封装的变迁,以及近几年手机产业推动的HDI技术兴起,包括近期Intel推出的Menlow平台,更是把HDI技术带到了PC行业。

面对PCB设计的密度的不断提升,PCB工程师必须紧跟业界前沿,了解新材料、新工艺,采用能支撑高密PCB设计的一流EDA软件,这样才能满足产品研发过程中面临的密度越来越高的挑战。据称,即将推出的PSD 16.2在HDI的设计上将有较大的突破,期待中。

5.电源、地噪声的挑战

电源、地平面作为信号线的参考平面、回流通道,电源、地的噪声会直接串入以其为参考平面的信号。解决电源、地噪声的问题,不仅仅是考虑供电电源的自身电平稳定问题,还是解决高速信号的可靠性问题的重要因素。

高速PCB的电源设计首先要理清电源树,分析电源通道合理性。

首先,在大电流的载流能力上,必须在考虑裕量的前提下分配恰当的布线宽度;同时,因为实际布线有电阻,从电源输出端到实际负载的路线上有压降,而高 速电路器件的电压特别是core电压往往很低,压降对供电效果有直接的影响。电流的载流能力,与线宽、内外层、铜厚度、允许温升相关。

其次,在电源的滤波效果上,需要考虑电源的阻抗。因为电源通道实际上不是一个理想的通道,而是有电阻和阻抗的,高速电路在门电路翻转时需要瞬间的电源供给,而电流从电源模块给各个门电路翻转提供能量是需要各级路径分配的,需要时间,这可理解为一个分级充电的过程,

图6:门电路翻转供电路径

可以看到,在高频状态下,器件管脚上的电流首先是由电源、地平面组成的平板电容来供电的,因为由他们组成的供电系统阻抗最低。供电速度最快,但是, 这个平板电容存储的电量太小,他们的电荷由小的滤波电容提供,小滤波电容的电荷再由大的BULK储能电容提供,然后开关电源通过电流通道给BULK电容充 电,之所以这样,是因为开关电源仅在几K的频率下是低阻抗的、BULK电容仅在几兆的频率下是低阻抗的,小滤波电容仅在几十兆到几百兆的频率下是低阻抗 的,电流只有通过层层充电,才能到达器件管脚,满足瞬时供电的需要。Cadence也提供了一个PI分析模块,来分析在不同的功耗下电源平面的阻抗,以及 滤波电容的选择是否合理。