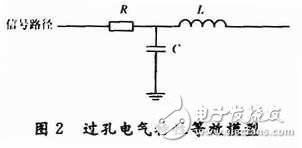

过孔作为一段特殊的传输线,在高速电路中,过孔不但产生对地的寄生电容,同时也存在着寄生电感,其电气特性的等效模型如图2所示。

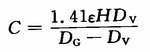

过孔的寄生电容给电路造成的影响主要是使数字信号上升沿减慢或变差,降低了电路的速度。过孔的寄生电容值越小,影响越小。若过孔在铺底层上的隔离孔直径为DG,过孔焊盘的直径为Dv,PCB厚度为H,板基材料介电常数为ε,则过孔寄生电容C的大小近似于:

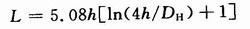

过孔寄生电感的主要影响是降低了电源旁路电容的有效性,使整个电源供电滤波效果变差。若L为过孔的寄生电感,h是过孔的长度,DH是中心钻孔的直径,则可以用下面的公式来简单计算一个过孔近似的寄生电感:

从上式可以看出,过孔直径对电感的影响较小,过孔长度对电感影响较大。在PCB中,通常旁路电容一端通过一个通孔连接到地平面,另一端也通过一个通孔连接到电源平面,因此通孔电感的影响会增加1倍。

2.3 传输线拐角对传输通道信号完整性问题的贡献

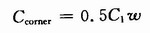

当信号沿均匀连线传播时,不会产生反射和传输信号的失真。但传输线上的拐角会使传输线处的阻抗发生变化,致使信号出现部分反射和失真。根据导线单位长度电容C1(单位:pF/in),导线线宽ω(单位:in),可通过下面公式简单估算每个拐角的寄生电容Ccorner:

在高密度电路板中信号线线宽较窄时,其拐角的寄生电容量引起的时延累加一般不太可能对信号完整性有很大影响。但对于高频敏感电路,如高频时钟线路,应考虑拐角寄生电容所产生的累加效应。

3 利用布线技巧抑制信号完整性问题

当信号从驱动源输出时,构成信号的电流和电压将互连线看作一个阻抗网络。当信号沿阻抗网络传播时,它不断感受到互连线所引起的瞬态阻抗变化。如果信号感受到的阻抗保持不变,则信号不失真。一旦阻抗发生变化,信号就会在变化处产生反射,并在通过互连线的剩余部分时发生失真。如果阻抗改变程度足够大,失真就会导致错误的触发。在信号完整性优化设计过程中,一个重要的设计目标就是:将所有的互连线都设计成均匀传输线,并减少所有非均匀传输线的长度,让整个网络中的信号所感受到的阻抗保持不变。基于此,可以归结出一些利用布线技巧抑制信号完整性问题的方法:印制导线的走线形状不要缠结、分支或硬拐角,尽量避免T形线和桩线;尽量保持同一网络信号线的线宽,减少线宽变化;减少传输线长度,增大导线宽度;要尽量增大导线间的距离;尽量减少高速信号线的过孔及拐角,减少信号线的层间转换;合理选择过孔的尺寸大小;减小信号环路面积及环路电流。总之,任何改变横截面或网络几何形状的特征都会改变信号所感受到的阻抗。布线中减少信号完整性问题的重点就是减少传输线上的阻抗突变,让整个网络中的信号所感受到的阻抗保持不变。