今天小编要和大家分享的是EDA,IC设计相关信息,接下来我将从PCB Layout抑制串扰的3W线距原则,mt781x pcb layout注意事项及emi测试注意事项-20131219这几个方面来介绍。

EDA,IC设计相关技术文章PCB Layout抑制串扰的3W线距原则

串扰(Crosstalk)是指信号线之间由于互容(信号线之间的空气介质相当于容性负载),互感(高频信号的电磁场相互耦合)而产生的干扰,由于这种耦合的存在,当一些信号电平发生变化的时候,在附近的信号线上就会感应出电压(噪声),在电路设计中,抑制串扰最简单的方法就是在PCB Layout中遵循3W原则。

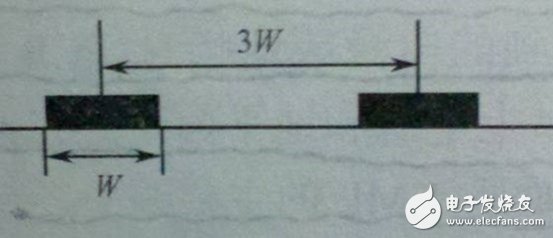

3W原则是指多个高速信号线长距离走线的时候,其间距应该遵循3W原则,如下图1所示,3W原则要求相邻信号线中心距离不能少于线宽的3倍,据一些资料记载的,满足3W原则能使信号间的串扰减少70%。我们在对高速信号,例如DDR3,PCIE,SATA2等布线的时候都会遵循这个原则。

图1

图2

关于EDA,IC设计就介绍完了,您有什么想法可以联系小编。