图 6 ads129x.ibs 文件 C_comp 值模型 DIO_33 列表

图 7 端接-校正策略

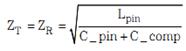

输入和输出阻抗对信号传输至关重要。下列方程式定义了 IBIS 模型引脚的特性阻抗:

(6)

(6)

输出升降时间

在整个行业中,升降时间规范的惯例是使用输出信号在 10% 和 90% 轨至轨信号之间摆动所需的时间,其一般为 0 到 DVDD。“IBIS 开放式论坛”的升时间定义相同,其获得采用是由于 CMOS 开关波形尾部较长。

IBIS 模型内的输出、I/O 和三态模型,有一些位于“[Ramp]”关键字下面的规范,该关键字针对 R_load (test load)、dV/dt_r (rise time) 和 dV/dt_f (fall time)。升降时间数据范围为电压-输出信号的 20% 到 80%。如果典型 dV/dt_r 值的分母乘以 0.8/0.6,则升时间值将在 20%-80% 摆动到 10%-90%摆 动之间变化。请注意,该数据代表一个电阻性负载 (R_load) 的缓冲器。ads129x.ibs 文件中,DIO_33 数据假设为一个 50-Ω 负载,因此该数据未达到 DVDD。该计算产生的数值,为各种传输线计算提供了正确的 tRise 值,例如 fKnee、f3dB 和升沿长度。

利用 IBIS 设计传输线

本文以讨论一个错配端接阻抗的 PCB 作为开始。之后,我们通过 IBIS 模型,了解和查找这种传输问题的一些关键组成元素。就此而言,这种问题应该有解决的方案。图 7 显示了端接校正策略,而图 8 则显示了校正之后的波形。

图 8 端接校正的稳定信号

若想设计 PCB 传输线,第一个步骤便是从产品说明书收集资料。第二个步骤是检查 IBIS 模型,找到无法从说明书中获取的一些参数—输入/输出阻抗、升时间和输入/输出电容。在进入到硬件阶段,需利用 IBIS 模型找到一些关键的产品规范,并对最终设计进行仿真。

关于EDA,IC设计就介绍完了,您有什么想法可以联系小编。