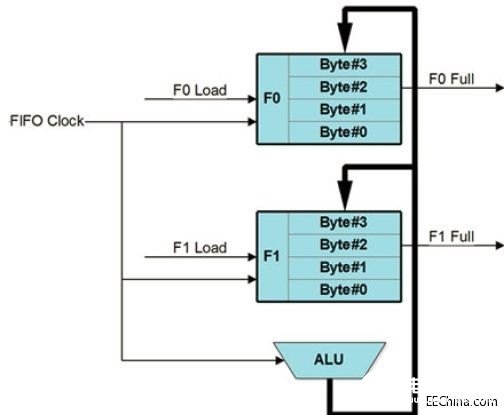

图9:针对8字节FIFO的数据路径配置。

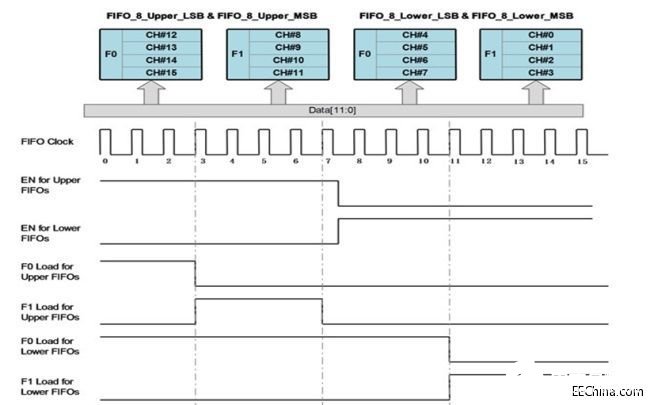

图10所示的是FIFO的工作时序。12位SAR结果分别存储在LSB_FIFO和MSB_FIFO中。Count7单元可对从15到0的通道进行排序。因此通道15到8存储于FIFO上部,通道7到0存储于FIFO下部。加载信号根据FULL状态和启用信号而生成。

图10:FIFO时序。

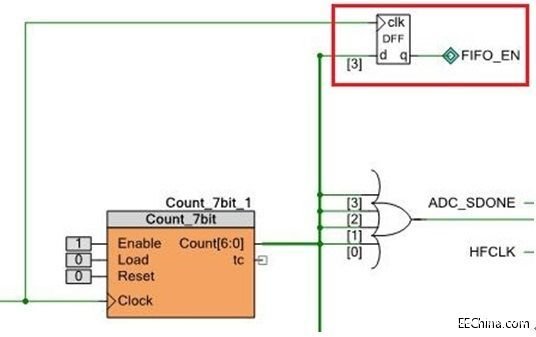

最后四个通道的结果一旦存储完毕后就会触发ISR读取FIFO。FIFO Enable使用Count7单元的位(如图11的红色部分所示),同时该位也与SWITCH_CLK(SDONE)同步。这样可确保EN变化不会破坏FIFO采样。

图11:为FIFO生成EN的详细设计。

设计测试

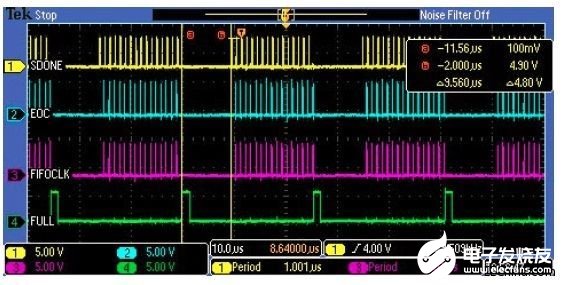

图12所示的是一个采样周期。十六个SDONE和EOC脉冲表示通道转换。十六个FIFOCLK和一个FIFO的FULL信号可对最后四个结果进行缓冲,用于说明FIFO的工作状态。请注意,SDONE和FIFOCLK之间的间隔是1μs。

图12:测试结果——一个采样周期中的信号。

图13是多个采样周期的波形。将数据从FIFO存储到SRAM的两个周期之间的间隔是大约9.56μs。

图13:测试结果——多个采样周期。

责任编辑:gt

关于模拟技术就介绍完了,您有什么想法可以联系小编。