2 SAR ADC概述

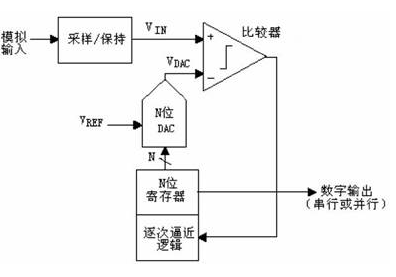

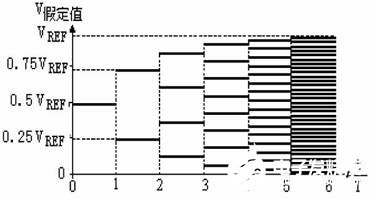

实现逐次逼近式ADC 的方式千差万别, 但其基本结构非常简单。如图1 所示, 模拟输入电压( VIN) 由采样/ 保持电路保持。如图2 所示, 为实现二进制算法, N 位寄存器首先设置在中间刻度( 即:100 …….00, MSB 位1) 。这样, 数字模拟转换器( DAC) 输出( VDAC) 被设为VREF/2, VDAC 是提供给ADC 的基准电压。然后, 比较判断VIN 是小于还是大于VDAC.如果, VIN》VDAC, 则比较器输出逻辑高电平或1, N 位寄存器的MSB 保持为1.相反, 如果VIN 《 VDAC, 则比较器输出逻辑低电平, N位寄存器的MSB 清为0.随后, 逐次逼近控制逻辑移至下一位, 并将该位设置为高电平, 进行下一次比较。这个过程一直持续到最低有效位( LSB) 。上述操作结束后就完成了转换, N 位转换结果储存在寄存器内。

图1 N位逐次逼近A/ D 转换器的结构图

图2 A/ D 转换器的逐次逼近过程

3 数字校准算法

目前, 工业界的SARADC 产品以二进制加权电容阵列、分段电容和RC 混合结构三种结构为主, 精度从10 位到18 位不等。其中, 二进制加权电容阵列构成的SARADC 由于低功耗的优势应用更为广泛。

由于CMOS 工艺的限制, 无源器件的匹配精度不高, 二进制加权电容阵列SARADC 转换器只能达到12 位精度。利用激光修正等技术, 可以提高无源器件的匹配精度, 但是成本较高, 不适于工业生产。因此, 提出了各种自校准方法, 以提高无源器件的匹配精度, 从而提高转换精度。如使用失调子DAC 和校准子DAC 预先对主DAC 的低位充电, 以达到校准的目的; 或使用多位非二进制加权电容DAC 和自校准算法, 使电容匹配达到较高的精度。

数字校准技术的意义即在ADC 正常使用前, 利用ADC 的已有电路对芯片的非线性因素进行测试,通过一定算法并根据ADC 使用时的时序产生相应的校准码, 加之于存储器中, 在ADC 工作时通过数字控制逻辑将所存校准数据对应加载到电路中, 从而达到校准失配的目的。对于本次SARADC 的设计, 我们采用结构对称的两组18 位电容阵列数模转换器( DAC) 输入至比较器的正负输入端( 准差分结构) , 如图3, 这种对称输入可以使比较器正负两端输入负载相等, 另一方面, 两电容阵列的高位DAC 可对全差分信号进行采样, 并输出全差分的参考电压, 而电容阵列I 的低位作为正常的低位子DAC 使用产生SAR 所需的参考电压, 电容阵列II的低位则用于测量和校准两组电容阵列高位的非线性。