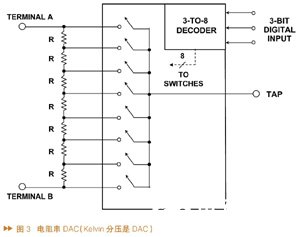

如果去掉图3电阻串DAC最上面的电阻,梯形电阻串的上下两个端点就变成了电位器的两个端点,从而得到数字电位器,电阻串DAC的输出成为了电位器的抽头。

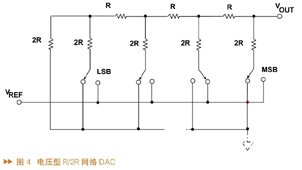

基于R/2R网络的DAC一直是一种普遍使用的类型,由于2:1比率很低,因此电阻非常容易制造以及微调,如图4所示为一个电压型R/2R阶梯网络DAC。该架构中每个二进制位在地与基准电压之间切换,其中一个有利的特点是该架构输出阻抗与代码无关,是恒定的。其输出可以为电压,或者是流入虚地的电流。需注意的是,这些开关必须能工作在很大的共模电压范围(从VREF到地电位)内,而且VREF端点的阻抗是输入数字量代码的函数,因而必须用低阻抗驱动。

对于R/2R阶梯DAC电流型输出结构,其开关总是工作在地电位。由于这种架构如果使用CMOS开关,则VREF输入可以有正极性或者负极性。如果把双极性AC输入加到VREF引脚上,就有4象限乘法,因此可以得到VREF电压与数字量代码之间乘积的输出,因此这种DAC架构通常被用于乘法DAC(MDAC)中,可以应用到以数字控制方式对信号进行放大或缩小。

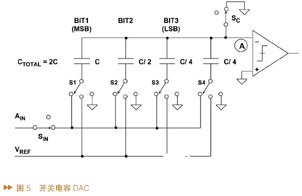

如果用电容切换代替电阻或电流源,即为开关电容DAC或称电荷分配DAC,如图5所示。其中电容的匹配是用精密光刻技术控制的,并且还另外增加了一些电容和开关出厂前的微调,或者在完成安装之后的系统级自校准调试过程中使用。而该架构的一个缺点是,开关时的瞬态电流注入到模拟输入端,这需要驱动放大器对于这些瞬态电流能够在大约半个转换周期内稳定下来。

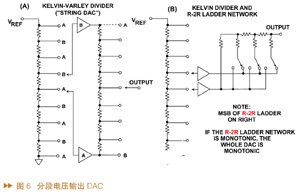

若干个低分辨率DAC可以使用“分段(segmentation)”技术组合成较高分辨率的DAC,有许多种方法可以实现这种分段。如图6中(A)所示,两个3位电阻串DAC构成一个完整的6位DAC,如果采用CMOS工艺,这种DAC效果很好。其中,最高的几位是用第一个电阻串DAC实现,而最低的几位用第二个电阻串DAC实现。而在图6(B)中,低位DAC是用二进制DAC构成的。分段法降低了开关毛刺的影响,有助于减少与数字输入有关的DNL误差,因此常用于高速DAC中。