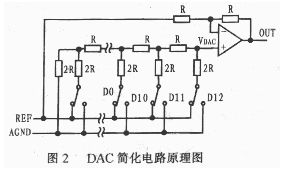

图2中,DAC梯形网络的输出由增益为2的运算放大器缓冲。所有缓冲放大器的反相结点连接各自的基准电压输入端REF。这样双极性电压输出范围可以-REF~+REF(4095/4096)。

3.2MAX547工作时序

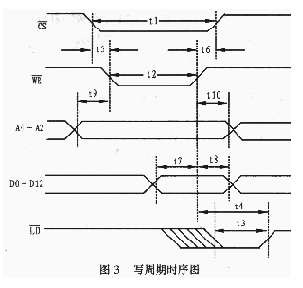

驱动MAX547的异步输入LD信号可将数据从输入锁存器传送到DAC锁存器。DAC锁存器的数据用来设置输出电压。所有输入端的控制逻辑均通过电平触发实现。数据可以锁存也可以直接传送给DAC锁存器。由CS和WR信号共同控制输入锁存器。LD信号用于控制数据从输入锁存器传送到DAC锁存器。当CS和WR信号同时为逻辑低电平时,输入锁存器打开;当LD信号为逻辑低电平时,DAC锁存器打开,在CS和WR为低电平期间,地址线A0,A1,A2必须有效,如图3所示。否则,数据会被写进错误的DAC。当CS和WR两信号中有一个为逻辑高电平时,数据将锁存在输入锁存器,在LD信号翻传至逻辑高电平的瞬间,MAX547再把数据锁存至DAC锁存器。若CS和WR信号为逻辑低电平,LD信号出被置为逻辑低电平,要实现数据正确传送,LD信号必须在CS和WR信号失效后持续t3或更长时间的逻辑低电平,如图3所示。驱异步CLR信号至逻辑低电平可使所有DAC的输出端复位到模似地电平,而与此时CS、WR、LD端输入信号的状态无关。在CLR信号翻转至逻辑高电平的瞬间,数据1000H都被锁存至所有的输入锁存器和DAC锁存器中。

4.与MCS8051单片机的接口电路

MAX547与8051单片机的接口电路如图4所示。由于MAX547有13位输入位,而8051单片机只有8根数据线,所以单片机需分两次发送要转换的某一数据,因此,电路中选用了74LS377作为数据锁存器。它的相关指令如下:

假设选择0通道(A2A1A0=000B),转换数暂存R1(高5位)和R0(低8位)中,则程序如下:

MOV DPTR,#8000H

MOV A,R0

MOVX A,@DPTR ;选中锁存器74LS377,并锁存低8位。

CLR P1.0;DAC A的锁存器透明。

MOV DPTR,#0000H

MOV A,R1

MOVX A,@DPTR ;选中MAX547及0通道,转换数送入DACA的输入锁存器

NOP

SETB P1.0 ;转换数送入DAC A锁存器,同时输出结果。

如果要获得±2.5V的满量程输出电压摆幅,可以选用MAX873作基准,它可以同时驱动全部4个基准输入端。若想获得一个±4.096V的输出电压摆幅(1LSB=1mV),可以选用MAX676,它在+5V电源下足以驱动2个基准输入端。