另外,MAX194自身具有校准功能,可在上电时进行校准。当外部环境改变时(如温度变化,电源电压改变等),还可以人为地置RESET为0时进行校准。

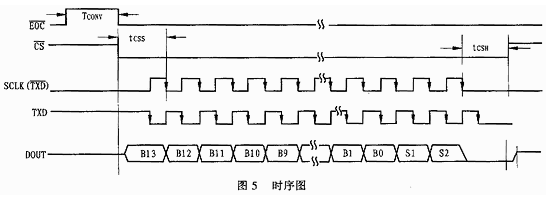

2 管脚排列及功能

MAX194的管脚排列如图3所示。它采用16脚DIP封装,各管脚的功能如下:

引脚1(BP/UP/SHDN)为三态输入,此脚悬空,则模拟信号以双极性方式输入;接高电平时以单极性输入;接低电平时则以10μA的关闭模式工作。

引脚10(RESET)接低电平时停止工作,并在上升沿开始校准。

引脚9(CONV)变低后,A/D转换开始。

引脚7(EOC)为转换结束输出。转换结束时输出低电平,到一下次转换开始时再变成高电平。

引脚2(CLK)外接转换时钟,最大频率为1.7MHz;引脚3(SCLK)如果在转换结束后读取结果,则以SCLK的频率读取。它可以与CLK的频率不同,最大为5MHz。

引脚5(DOUT)为串行数据输出脚,先输出最高位。

引脚8(CS)为片选信号,允许串行输出。

引脚12(REF)为参考电压输入端,输出范围为0~5V。

引脚11(AIN)为模拟输入,输入范围为0~VRFEF或-VREF~+VREF。

引脚6,14(DNCD,AGND)分别为数字地,模拟地。

引脚4,16(VDDD,VDDA)分别为+5V数字电源,+5V模拟电源。

引脚11,15(VSSD,VSSA)分别为-5V数字电源,-5V模拟电源。

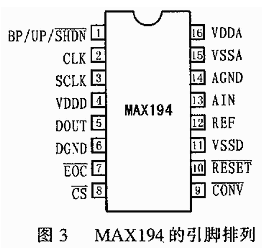

3 MAX194的应用电路

MAX194可广泛应用于工业控制,测量,数字信号处理等方面。

图4为笔者在锅炉测温系统中用MAX194与单睡机进行接口的接口电路,该接口将CS接P2.7脚,并由软件发出片选信号。用于转换的时间脉冲CLK由89C51的ALE脚产生。89C51的TXD经非门接SCLK,以用做读取数据的时钟。

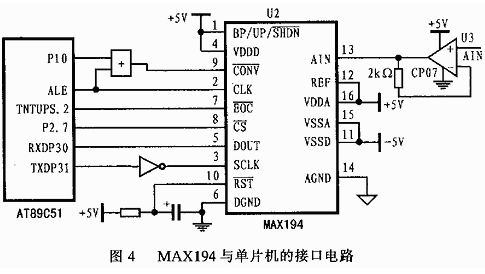

读出转换结果有两种方式,一种是在转换的过程中以CLK的时钟频率读出,另一种是在转换结束后以SCLK的时钟频率读出。笔者选择在转换结束后读取结果的方式(第二种)。该方式在转换结束以后,当EOC变低并且在CS也为低时,在DOUT上输出最高位,之后在SCLK的下降沿依次输出其它位。SCLK允许的最高频率是5MHz。图5为其时序图。

图中,tCONV为转换时间;tCSS为CS下降模沿的时间;tCSH为SCLK最后一个下降沿至CS上升沿的时间。