3.2 数字部分

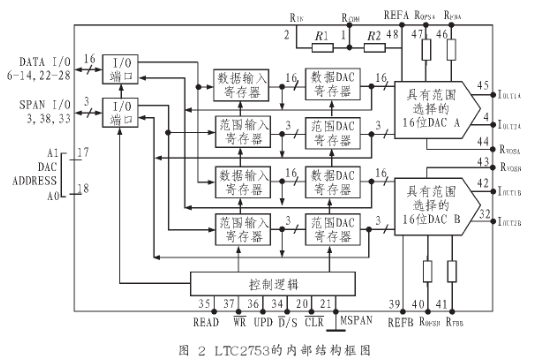

LTC2753的每个DAC都有4个内部寄存器,共有8个寄存器,如图2所示。每个DCC通道都有2组双缓冲寄存器,一组用于寄存数据,一组用于寄存输出范围。双缓冲寄存器具有同步更新范围和编码功能。当改变电压输出范围时,双缓冲功能使电压平滑转换,无毛刺产生。乘法DAC同步更新。每组双缓冲寄存器是由输入寄存器和DAC寄存器组成。输入寄存器为保持寄存器,当数据载入输入寄存器需经过一个写操作,而DAC输出不受影响。另一方面,DAC寄存器直接控制DAC输出电压或输出范围,将与其连接的输入寄存器中的内容复制到DAC寄存器,改变DAC寄存器内容,则需经过一个更新操作。

3.3 写和更新操作

执行一次写操作:将D/S引脚与WR引脚置低,直接通过16位微处理器总线将数据写入输入寄存器。UPD引脚置高,将输入寄存器储存的数据复制到DAC寄存器,完成一次更新操作。数据与范围同时更新;除非输入寄存器的值先经一个写操作被改变,否则DAC寄存器的值不会改变。

范围输入寄存器的载入:将D/S引脚置高,WR引脚置低。除了并行位的个数不同外,范围寄存器与数据寄存器结构相同。范围寄存器有3位,而数据寄存器有12、14或16位。若要数据寄存器和范围寄存器在工作模式下保持透明,则要将WR引脚置低,UPD置高,阻止了输出干扰脉冲的增加。限变器在UPD引脚的上升沿有效。

当WR和UPD连在一起由一单时钟信号驱动时,输入寄存器和DAC寄存器则以主从支配关系,或是边沿触发、配置的模式工作。在时钟的下降沿,数据位存入输入寄存器,随着时钟上升沿的到来,进入DAC寄存器。

SPAN引脚S2~SO用数据LSB共享数据,同时将数据和范围控制在一个16位数据总线上,范围和数据不能同时进行写或读操作。

异步CLR引脚在任何输出范围内都可将DAC输出清除至O V,CLR对所有数据寄存器复位,而不干扰范围寄存器。

这些装置也可通过上电复位将DAC的输出电压在任何输出范围初始化至0 V。如果是软件范围配置,DAC上电至0~5 V之间;若是手动范围,DAC采用适当编码,选用手动上电。

3.4 手动范围配置

若要配置LTC2753为单范围,将MSPAN引脚置高,D/S引脚置地。通常,要求的输出范围由SPAN I/O引脚(S2~SO)设定,但通过直接接地或接电源编程设置的,如图3所示。在这个配置中,DAC的通道都可以在上电时对选择的输出范围初始化。当设定手动范围操作时,SPAN引脚的回读功能无效。