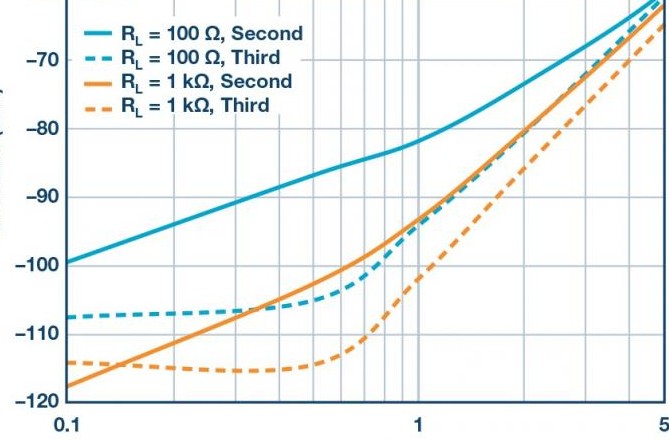

为了更好地阐述上面的观点,图5显示了放大器驱动不同阻性负载的性能差异。图6显示了容性负载引起的小信号过冲,这会影响建立时间和线性度。

图5.AD4896-2 THD性能与负载的关系

图6.ADA4896-2的小信号传输响应与负载的关系

为了最大限度地解决这个问题,放大器输出应通过低通滤波器的串联电阻与外部电容隔离。

电阻应足够大,以保证缓冲器不会看到虚部阻抗,但又足够小,以满足所需的输入系统带宽,并使缓冲器流出的电流在电阻上引起的IR压降最小(放大器可能无法足够快地使这种电压降稳定下来)。同时,电阻应支持外部电容减小到足够小的值,以最小化反冲而不影响建立时间。

您可以在这里找到更多信息。

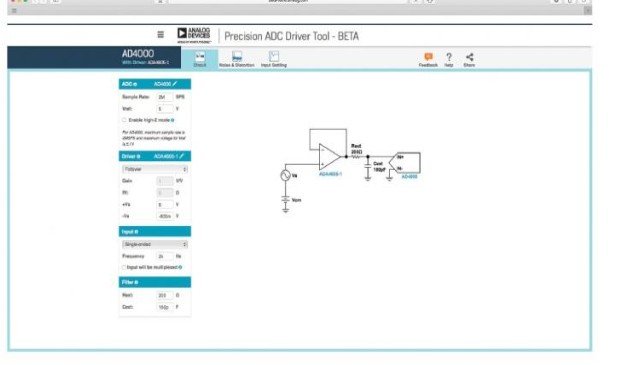

幸运的是,有一些工具可以让我们预测ADC、放大器和滤波器的组合性能,比如说精密ADC驱动器工具。

此工具可以对反冲、噪声和失真性能进行仿真,如图7所示。

图7.精密ADC驱动器工具的各种仿真

低通滤波器的经验法则

通常,一阶低通滤波器出现在许多建议中,但为什么没有人使用更高阶滤波器?除非应用明确要求消除输入信号中较大的带外干扰或谐波,否则增加滤波器阶数将给系统带来额外的复杂性。一般来说,折衷方案是让小信号带宽略高于需求,这会影响噪声,但好处是能够轻松驱动ADC输入级,并能降低功耗和成本。

减轻负担

我们之前提到,放大器不喜欢虚部阻抗和/或提供大电流,但这不可避免,因为虚部阻抗是电容带来的,而电容能解决反冲问题。

改善这种情况的唯一办法是减少反冲。这种解决方案已被最新的ADI转换器采用,例如AD7768和AD4000。

由于转换器架构不同,每种器件采用的解决方案也不同。AD4000 SAR ADC可在低于模拟输入范围的电源下工作。采用的解决方案称为高阻模式,仅适用于100kHz以下的采样频率。

在AD7768中,电源等于或高于模拟输入范围。AD7768采用的解决方案称为预充电缓冲器,与高阻模式相反,其工作频率最高可达ADC最大采样频率。

两种解决方案均基于相同的工作原理,驱动ADC的主要困难是电容电荷再分配。换句话说,当内部开关重新连接采样电容时,输入缓冲器和低通滤波器看到的电压降越低,电压反冲就越小,ADC输入电流相应减小。因此,驱动ADC就越容易,建立时间也越短。滤波器电阻上的压降降低,故交流性能得到提升。