NVIC提供如下的功能:

可嵌套中断支持

向量中断支持

动态优先级调整支持

中断延迟大大缩短

中断可屏蔽

可嵌套中断支持: 可嵌套中断支持的作用范围很广,覆盖了所有的外部中断和绝大多数系统异常。外在表现是,这些异常都可以被赋予不同的优先级。当前优先级被存储在 xPSR 的专用字段中。当一个异常发生时,硬件会自动比较该异常的优先级是否比当前的异常优先级更高。如果发现来了更高优先级的异常,处理器就会中断当前的中断服务例程(或者是普通程序),而服务新来的异常——即立即抢占。

向量中断支持: 当开始响应一个中断后,CM3会自动定位一张向量表,并且根据中断号从表中找出 ISR的入口地址,然后跳转过去执行。不需要像以前的 ARM那样,由软件来分辨到底是哪个中断发生了,也无需半导体厂商提供私有的中断控制器来完成这种工作。这么一来,中断延迟时间大为缩短。

(5)存储器映射

Cortex-M3支持4G存储空间,具体分配如下图:

(6)总线接口

Cortex-M3内部有若干个总线接口,以使 CM3能同时取址和访内(访问内存),它们是:

指令存储区总线(两条)

系统总线

私有外设总线

有两条代码存储区总线负责对代码存储区的访问,分别是 I-Code 总线和 D-Code 总线。前者用于取指,后者用于查表等操作,它们按最佳执行速度进行优化。

系统总线用于访问内存和外设,覆盖的区域包括 SRAM,片上外设,片外 RAM,片外扩展设备,以及系统级存储区的部分空间。

私有外设总线负责一部分私有外设的访问,主要就是访问调试组件。它们也在系统级存储区。

(7)存储器保护单元(MPU)

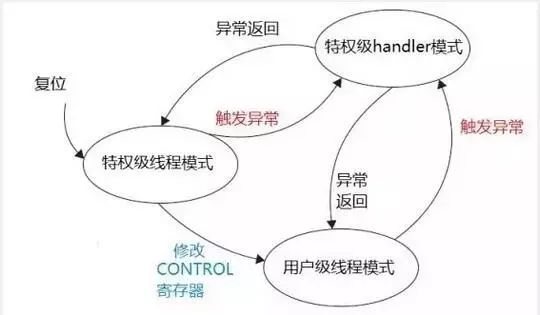

Cortex-M3有一个可选的存储器保护单元。配上它之后,就可以对特权级访问和用户级访问分别施加不同的访问限制。当检测到犯规(violated)时,MPU 就会产生一个 fault 异常,可以由fault异常的服务例程来分析该错误,并且在可能时改正它。

MPU 有很多玩法。最常见的就是由操作系统使用 MPU,以使特权级代码的数据,包括操作系统本身的数据不被其它用户程序弄坏。MPU在保护内存时是按区管理的。它可以把某些内存 region设置成只读,从而避免了那里的内容意外被更改;还可以在多任务系统中把不同任务之间的数据区隔离。一句话,它会使嵌入式系统变得更加健壮,更加可靠(很多行业标准,尤其是航空的,就规定了必须使用 MPU来行使保护职能——译注) 。