图6:3D NAND的R&D 技术蓝图。(图片出自:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.)

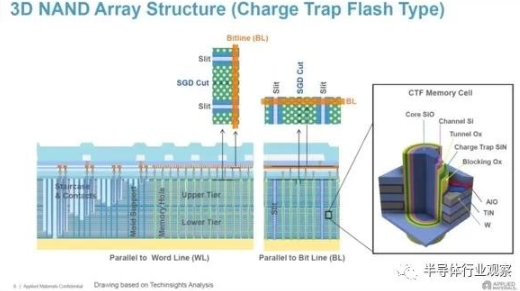

图7:Charge Trap方式--具有代表意义的3D NAND。(图片出自:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.)

为了实现以上这些多层化,如图6下部所示的研发是必不可缺的。首先, 就左侧的“Architecture Change”而言,会把CMOS线路配置在存储单元格(Memory Cell)的下面(CUA),或者像YMTC的做法一样采取Bonding的方式,增大单个芯片的面积上的存储密度。这种技术已经被多个NAND厂家采用。

所谓的“Vertical Scaling”技术,指的是在纵向可以堆叠多少层的存储单元。此图中清晰地写着未来的发展趋势。首先,有一个单纯地增加存储单元格(Cell)数量的“More Pairs”。其次,有一个“WL(Ward Line)Pitch Reduction”(三星已经采用此项技术)。这是一种纵向收缩存储单元格尺寸的技术方法。运用此技术,如果是同样的Pair数量,由于可以降低Stack Height,内存孔(Memory Hole)的HARC加工将会变得很容易。

此外,如果同时进行“WL Pitch Reduction”和“More Pairs”,迟早会出现“Multi Tiers”(多层堆叠)。三星以外的厂家已经运用到量产产品中。笔者认为,未来三星肯定也会转移到“Multi Tiers”(多层堆叠)。此外,笔者还认为,所有的NAND厂家未来都为朝着堆叠双层、三层、四层甚至更多的方向发展。

另外,作为扩大存储密度的方法,还有一种是“Lateral Scaling”。这是一种通过横向收缩的方式,来扩大单个芯片存储密度的技术手段。“Lateral Scaling”有两种方式,其一为“More Holes b/w Slits”,即将Slit和Slit之间的内存孔的数量由现在的九个增加至十四个。其二为“Hole BL(Bit Line) Pitch Reduction”,即缩小存储孔的直径,使存储孔的密度更高。

但是,这两种研发都需要HARC蚀刻,此外,“More Pairs”的实行还存在很多复杂的问题,各家NAND厂家都需要在元件构造、材料、工艺流程等方面下工夫,在与生产设备厂家以及材料厂家共同研发的同时,推进存储半导体的高密度化。

另外,就像三星掌控了48层和64层、铠侠和WD掌控了96层一样,真正在高密度方面获得突破性发展的NAND厂家才能掌握新时代的霸权。究竟会花落谁家呢?也许我们能在下次在德国德累斯顿(Dresden)召开的IMW2021上看到端倪。笔者明年(2021年)还会继续参加IMW。