FIFO只允许两端一个写,一个读,因此FIFO是一种半共享式存储器。在双机系统中,只允许一个CPU往FIFO写数据,另一个CPU从FIFO读数据。而且,只要注意标志输出,空指示不写,满指示不读,就不会发生写入数据丢失和读出数据无效。

3.其他多端口存储器

以上只介绍了两种双端口存储器。随着电子工艺的飞速发展,出现了三端口及以上的存储器,并且在存储深度和宽度上得到很大发展,仲裁逻辑控制更加复杂;但多端口存储器源彼双端口存储器,基本更加复杂;但多端口存储器源自双端口存储器,基本工作原理入双端口存储器相似,这里不一一详述。

二、双口RAM实现数据采集系统

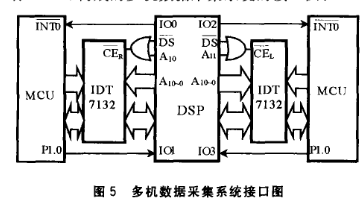

数字信号处理器(DSP)能实时快速地实现各种数字信号处理算法,而DSP的控制功能不强,可以采用8051单片机控制数据采集板,将采集的原始数据送给DSP处理并将处理结果传送给8位单片机。图5给出了利用1片数字信号处理器TMS320F206(以下简称DSP)和2片AT89C51单片机(以下简称MCU)构成多机数据采集系统接口图。

本系统采用两片CMOS静态双口RAM(IDT7132)实现MCU和DSP的数据双向传递。双口RAM作为DSP的片外数据存储器,即用外部数据存储器选通信号DS和高位地址信号经高速或门输出选通双口RAM的片选信号。这样可以利用DSP的重复操作指令(RPT)和数据存储器块移动指令(BLDD)减少数据传送时间,双口RAM的8位数据总线接在DSP的低8位。IDT7132的仲裁逻辑控制只提供Busy逻辑输出,而由于MCU无Busy功能,只能采用自行设计的软件协议仲裁方法。将双口RAM划分为两块:上行数据区(DSP接收MCU采集的数据区)和下地数据区(DSP输出处理结果区)。此处的上行数据区将远大于下行数据区。采用DSP的4个I/O口与MCU中断口和I/O口相连,并在数据区中规定一个信令交换单元。以DSP采集右端MCU上行数据为例,说明仲裁流程。

(1)初始化时,DSP置IO3为输出口,保持高电平,IO2为输入口(MCU使其初始化为低电平)。

(2)DSP需要采集MCU数据时,向右端IDT7132下行数据区的下行信令字单元(此处设为00H)写入需要取数的信令字,再向右端MCU发中断,置IO3为低电平,然后查询IO2等待MCU应答。

(3)MCU及时响应中断后,则先从IDT7132的下行数据区的下行信令字单元读取DSP请求信息,检测为DSP需要取数的下行信令。然后,向IDT7132上行数据区的上行信令字单元写入数据,准备好需要DSP取数据的信令(00H)或数据未准备好的信令(01H)。最后,向DSP发送应答信号,置IO2为高电平(此处高电平的持续时间不过长,只要DSP可以检测到即可)。