今天小编要和大家分享的是存储技术相关信息,接下来我将从基于CPLD技术和PCI总线技术实现数据接收和存储系统的设计,包邮 ●其核心由数字信号处理器及cpld组成,可以实现高性能的控制这几个方面来介绍。

存储技术相关技术文章基于CPLD技术和PCI总线技术实现数据接收和存储系统的设计

前言

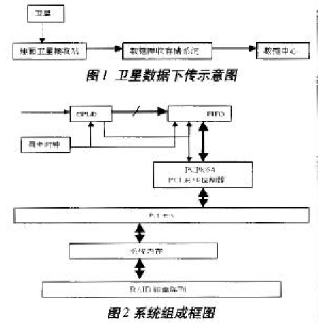

目前卫星技术已广泛应用于国民生产的各个方面。通讯卫星,气象卫星以及遥感卫星,科学探测卫星等与人们的生活密切相关。卫星所收集的大量数据资料能否及时准确地下传、接收和存储是卫星技术的一个重要方面。其传送过程如图1所示。

从卫星上高速下传的数据由地面卫星接收站转发为基带信号,通过光缆传送至数据中心,速度可达上百兆波特率,要求系统正确接收,经过同步和预处理,然后存入计算机系统,供数据中心使用。其特点是:数据下传速度高,数据量大,持续时间长,并且要求具有差错控制功能。而本文介绍了为了满足此要求而设计的数据接收和存储系统。

系统设计

数据接收和存储系统主要包括数据接收和预处理,数据传送,数据存储等部分。本文主要介绍CPLD,PCI总线结构,总线控制器PCI9054。其系统组成如图2所示。

基带串行信号由复杂可编程逻辑器件(CPLD)进行串并转换,变为8位数据信号后根据编码方式找到同步帧,并进行预处理,然后传到先入先出存储器FIFO, 在逻辑控制下将数据送入PCI总线控制器PCI9054,由9054采用DMA突发方式传输至内存,再存储到RAID磁盘阵列。

采用复杂可编程逻辑器件(CPLD)可大大减少复杂的控制,通过VHDL语言即可灵活设置控制逻辑。而且随着超大规模集成电路的发展,可编程逻辑器件的发展非常迅速,现已达到数十万门,速度《1ns(管脚之间)。由于高速电路设计中的干扰问题非常严重,因此要尽可能地减少线路设计,所以采用CPLD不仅可满足系统要求的复杂的逻辑关系,而且可大大减少布线干扰,调试和更改也非常方便,是今后逻辑控制的发展方向。在本系统中,CPLD不仅实现串并转换和同步的功能,同时还用以实现数据进入FIFO以及由FIFO传入PCI9054的传输控制逻辑,中断逻辑以及主机对数据传输通道的前端控制。