而目前市面上存在的网络测试仪主要有两种架构。

1、基于x86+DPDK+网卡的测试仪

X86的编程相对容易,调试手段更加丰富,成本有一定的优势,在要求不高的功能性测试方面,是一个不错的选择。

2、基于FPGA+x86混合的测试仪

FPGA+x86这样的软硬集合的测试系统,则适用于高性能、全覆盖、测试场景规模大、测试业务复杂的测试场景。

FPGA+x86的混合架构,一方面利用了FPGA越来越强大的数据层面硬件的并行性,另一方面也结合了CPU在控制层面的处理灵活性,同时由于FPGA和CPU本质上都是可编程的系统,根据业务处理的需要,可以在FPGA硬件和CPU软件之间灵活地移动业务划分边界,实现整个业务流程的全面优化。

我们按照前面所说的电信运营商的复杂测试场景要求,对两种架构的测试仪进行一个全面的对比分析如下:

1、64-16000字节包长的线速发流及统计能力

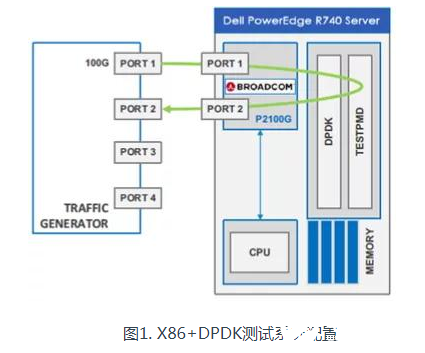

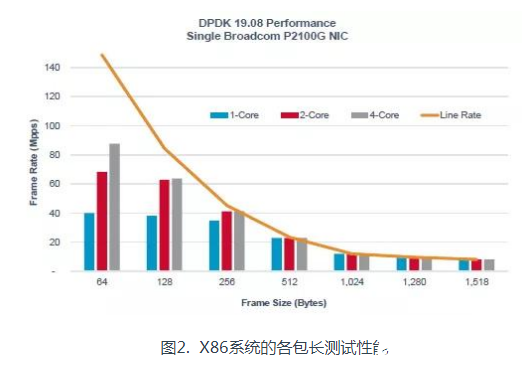

x86+DPDK+网卡:以图示的100G网络为例,在64字节包长的情况下,大概每秒会收发150M个数据包,以目前的CPU的计算和存储存取能力是无法处理的,而基于FPGA架构的测试仪没有此限制。根据DPDK官网公开发布的最新数据(2019.10.9)【数据来源,DPDK官网 www.dpdk.org】,采用图1的系统配置,可以明显看出在64,128,256等小字节情况下无法做到100G线速收发包;

FPGA+x86:所有字节可以做到线速发包与统计。

所能达到的小字节包长线速性能如图2所示。

2、时延和抖动的精确性

时延测试的精度在网络测试中是非常重要的指标。

x86+DPDK+网卡:X86系统是面向通用计算的系统,它本身的基准时钟精度就不高,同时OS的调度误差至少在us量级;如果x86系统的NIC不支持在物理层插入时间戳的话,需要由软件系统来处理网络时延,这将带来进一步的误差;所以通常网络测试需要的精确至10ns量级的时延难以在面向计算的通用x86平台上实现;

FPGA+x86:在FPGA平台上,通过0.1~0.001PPM精度的晶振,产生高达400M的时钟,可以将时延的精度控制在2.5ns数量级别。

3、存储系统灵活性

x86+DPDK+网卡:x86系统面向通用计算,目前主流的内存系统是DDR4内存,带宽大但是访问延迟也大,根据读写访问模式的不同,可能会带有延迟抖动;

FPGA+x86:FPGA的内存,可以根据需要组合片上RAM(可以实现cache功能)+DDR+QDR+RLDRAM等各种内存技术,优化带宽需求型和延迟需求型访问。