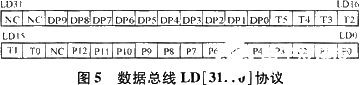

其中,P0~P12为脉冲重复周期码,T0~T5为提前量码,DP0~DP9为容差码,它们的计算精度均为1μs。

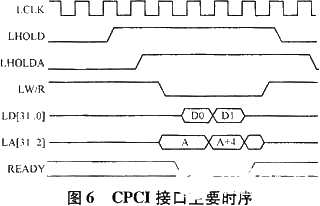

关于CPCI接口的主要时序关系见图6。

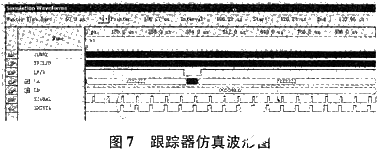

在Quartus4.1环境下,根据构建的FPGA逻辑电路,可以对跟踪器进行时序仿真,其仿真结果见图7。图中标注处为输入信号对应的输出波门,因为电路中引入了二级数字延时器,所以输出波门较输入信号延迟了2个信号周期。

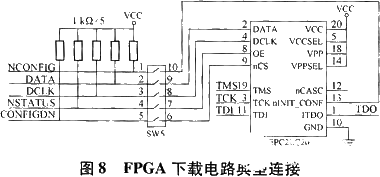

2.4 FPGA的配置芯片

FPGA配置芯片的选择主要根据FPGA配置文件的大小,同时参考FPGA生产厂家器件手册的推荐配置用法。几种常用的配置芯片容鼍大小如下:EPC2为1.6 Mbit,EPC4为4 Mbit,EPC8为8 Mbit,EPC16为16 Mbit,本跟踪器选择了EPC2Lc20芯片,它对应的下载电路连接方式参见图8。

2.5 跟踪器参数预置程序

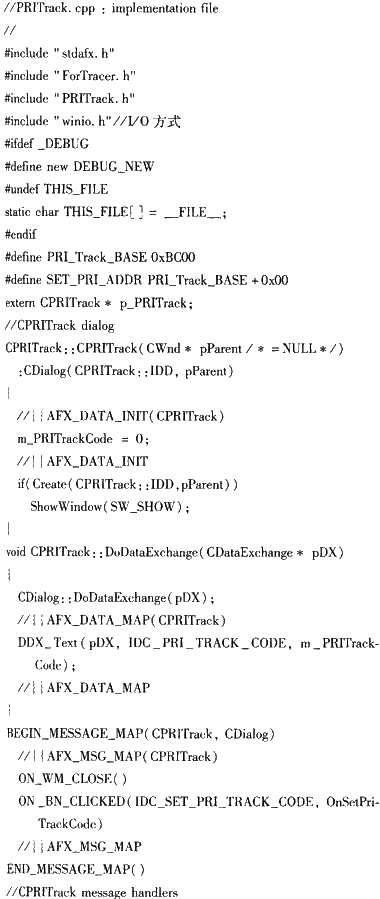

为了配合跟踪器的检验,可以在VC6.0环境下自行编制一个小型的跟踪器参数置数程序。

部分程序段格式及内容如下:

3、 结束语

本数字式重复频率跟踪器实现了在时域相关的基础上对一批相同重复频率脉冲信号的实时跟踪,通过改变各个功能模块的接口参数和对组合逻辑局部调整,可以得到电路特性指标允许范围内的理想的跟踪输出波门。未来的发展方向可以关注以下几点:脉宽相关、相位相关、可跟踪的信号批数(多批)、可跟踪的信号重复频率类型(重复频率P固定、抖动及参差)、对不同频率和不同方位信号的跟踪、跟踪波门精度的提高等。从而使跟踪器能够在密集信号环境中快速、准确地产生各种复杂信号的跟踪输出信号,实现对多批不同频率、不同方位、不同类型的目标分别进行有效实时跟踪的目的。