2.3 D/A转换模块设计

利用Texas Instruments公司的D/A芯片TLC5620,并辅助使用4输入与门SN74HC08M和运算放大器LM358AM,构建数模转换器。TLC5620是8位电压输出的数模转换器,需5V外接电压,有4个输出端口可以选择。利用扩展插槽与FPGA连接,信号接119脚,时钟由所编程序在FPGA内实现,通过73脚与TLC5620连接,控制信号通过63脚连接TLC5620。

3 、DSP Builder仿真和FPGA验证

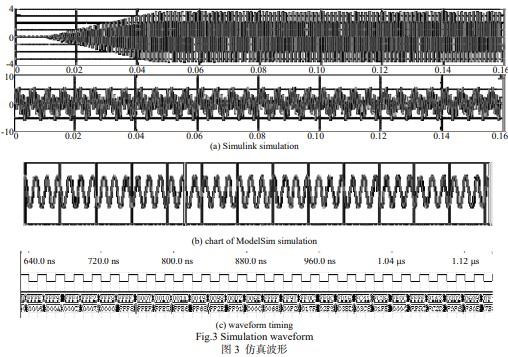

通过Simulink仿真得到波形,如图3(a)所示,图中第一行为返回A听筒的误差e信号波形,第二行为输入话筒的所有信号,即B信号与回波信号之和。由变化的波形可以看出,随着自适应滤波器的“学习”过程,回波逐渐被抵消。

利用ModelSim针对生成的RTL级VHDL代码进行功能仿真,设置信号为模拟形式,如图3(b)所示,图中为减去回波后的误差信号,与Simu-link仿真结果一致。

使用ModelSim完成RTL级功能仿真,其仿真结果并不能精确反映电路的全部硬件特性,进行门级的时序仿真仍然十分重要。在Quartus Ⅱ下编译后进行时序仿真,其仿真波形,如图3(c)所示。

把回波抵消器模型转化生成图元文件,作为一个子模块在顶层系统中调用。在QuartusⅡ环境下,调用各个子模块,构成完整的系统原理图设计,然后进行编译、仿真和引脚分配等工作。最后下载到FPGA芯片中,对硬件进行测试,采用SignalTapⅡ实际测得的值如图4所示,验证本设计的正确性。

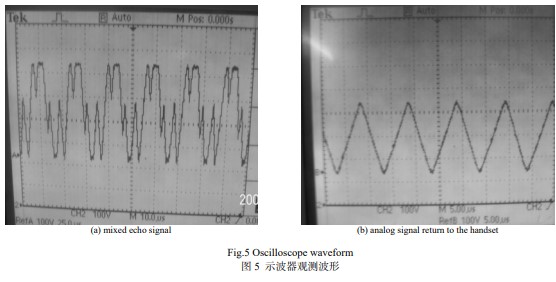

最后通过D/A转换电路接入示波器。观测结果,如图5(a),图5(b)所示,通过比较混合回波的信号和经过抵消后得到的返回听筒的消除回波以后的信号,可以看出回波已基本消除,设计达到目的。通过测试,回波衰减率约为25 dB,基本达到ITUTG.167标准中回波衰减率至少20 dB的要求。

4 、结束语

采用DSP Builder进行设计,使用图形界面,用模块化设计代替以往的VHDL语言编程,并综合多种设计工具,便于研究者迅速地将算法级的构思应用于系统设计中,从而可以专注于系统算法的设计,避免了繁琐的语言编程和电路设计,提高了设计速度,缩短设计周期,为产品开发节约了研发时间。

责任编辑:gt

关于FPGA,ASIC技术就介绍完了,您有什么想法可以联系小编。