值得注意的是,这里的bfloat16即Brain Float格式,而block float为块浮点算法,即当应用Block Float16及更低位宽块浮点格式时,指数位宽不变,小数位缩减到了16bit以内,因此浮点加法位宽变小,并且不需要使用浮点乘法单元,而是整数乘法和加法树即可,MLP的架构可以使这些格式下的算力倍增。

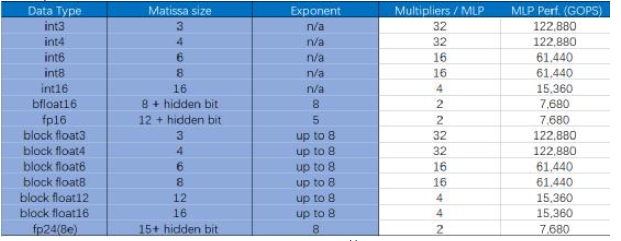

表3是Speedster7t系列1500器件所支持的典型格式下的算力对比,可以看到,单片FPGA的浮点算力最高可达到123TOPS。

表3 Achronix的Speedster7t系列1500器件支持的典型格式的算力对比

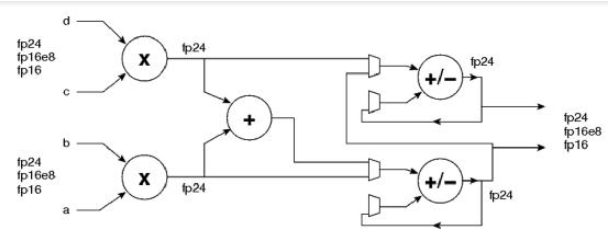

下图3是MLP中FP24/FP16乘加单元的简化结构图,即一个MLP支持FP24/FP16的A*B+C*D,或者A*B,C*D。

图3 MLP中FP24/FP16乘加单元的简化结构图

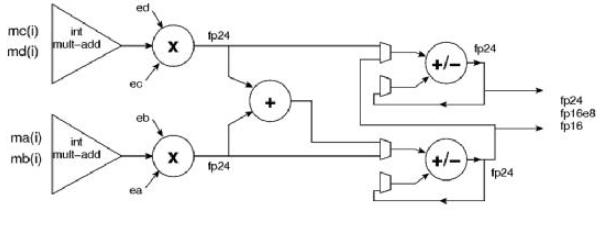

而以下的图4则是块浮点乘加单元结构。

图 4 块浮点乘加单元结构

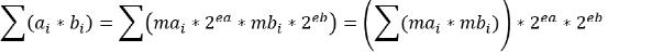

这里考虑浮点数序列块ai=mai∙2ea,浮点数序列块bi=mbi∙2eb,各序列块内均拥有相同的指数ea和eb。则

不难看出,乘法单元的个数取决于尾数(即整数)位宽。

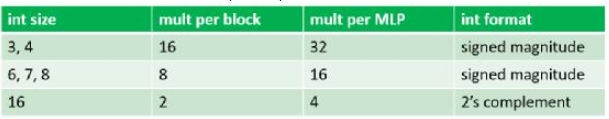

表4 MLP中乘法单元的个数与整数位宽的关系

关于可编程逻辑就介绍完了,您有什么想法可以联系小编。