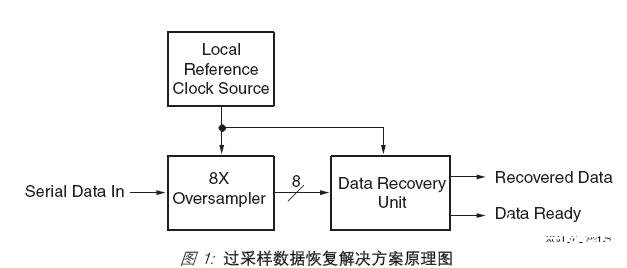

有多种方法可以在 Xilinx FPGA 中实现过采样器。可以将 RocketIO 收发器用作过采样器,在某些情况下以 1 Gb/s 或更高比特率进行过采样。实际上,一些 RocketIO 收发器内置了过采样接收器(称为数字接收器),所支持的比特率低于普通接收器。

在用 SelectIO 输入端接收异步串行比特流时,通常限制最大可支持比特率的是 FPGA 的最大时钟速率,而非 IOB 所支持的最大速率。因为过采样器必须在每个位周期内对比特流多次采样,所以采样时钟必须明显快于比特率。使用采样时钟的多个时钟相位,即可在不提高时钟频率的情况下增加每个位周期的样本数量,但是这种方法需要以某种方式精确地生成并分配多个时钟相位,而且会用尽多个全局时钟布线资源。例如,使用相互间隔 45 度的四个时钟相位,并且使用各时钟相位的两个边沿,就可以保证 8 倍过采样的基本时钟频率与比特率相同。

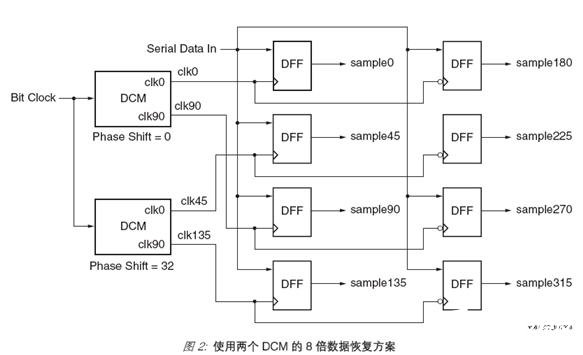

可以用 DCM 为串行输入的过采样创建多个时钟相位(参见 XAPP224 中的图2)。不过,根据时钟频率和每个位周期样本数不同,可能需要多个 DCM 才能提供足够的时钟相位。如果使用多个 DCM,这些 DCM 的输出就会在相互间产生相对抖动,这样就会降低采样点的精确性,从而降低接收器的抖动容限。图2 中使用的方案还要求与四个时钟相位对应的四个全局时钟。不过,如果所有比特率都相同,就可用这四个全局时钟来支持多个过采样器。

Xilinx 针对是否符合 SD-SDI 协议对多时钟相位过采样器进行了实验;因为支持的电缆长,这种协议要求位转换之间的行程长,抖动容限高。这些实验显示,任何低于 6X SD-SDI 比特流的过采样都无法提供足够的抖动容限,而 8 倍过采样是较为现实的下限。如图2 所示,使用四个时钟相位的 8 倍过采样方案需要两个 DCM。Xilinx 的实验显示,这两个 DCM 在时钟相位上产生的相对抖动将 DRU 的抖动容限降到了无法接受的程度。如果可以只使用一个 DCM,那么就能减轻时钟相位抖动问题,但仍然需要四个全局时钟。一个 Virtex-5 PLL 就可以生成四个低抖动的时钟相位,但仍需四个全局时钟将这四个时钟相位传送到过采样器。Virtex-4 器件不具备这种 PLL。