如第 4 页图3 所示,各样本通过由三个触发器构成的流水线送至主时钟域(零度时钟的上升沿)。第一触发器是采样触发器,偶尔会因为比特流异步采样而处于亚稳态。为了规避亚稳态引起的问题,本设计在流水线中第一与第二触发器之间至少让出四分之三时钟周期,以便给第一触发器留出时间在样本被时钟驱动进入第二触发器之前稳定下来。当样本被时钟驱动进入流水线中第三触发器时,样本已送入主时钟域,而且亚稳态已解除。

如果包括流水线中第一触发器上的延迟量,任何样本通过流水线的总延迟都恰好是两个时钟周期。以 315 度的样本为例,第一触发器使用 90 度时钟的下降沿,所以为该触发器被时钟驱动四分之三时钟周期。第一到第二触发器的延迟是四分之三时钟周期,而第二到第三触发器的延迟是半个时钟周期。加起来恰好是两个时钟周期。

与第 3 页图2 所示的双 DCM 技术相比,这种基于 IDELAY 的过采样技术在性能及资源使用方面都有优势。显然,这种技术少用了一个 DCM 和两个全局时钟。因为只使用一个 DCM,所以各时钟相位之间相对更稳定。因为 IDELAY 基元不会加剧抖动,所以各数据相位之间相对抖动甚微。因此,这种过采样技术可以提供更精准的可重复性比特流采样,并且可以提高接收器的抖动容限。

IDELAY 基元可提供每 tap 78 ps 的高精度延迟。延迟值 6 提供 468 ps 的延迟,非常接近 270Mb/s 位周期的八分之一 (463 ps)。270 Mb/s 是视频应用的常用比特率,在参考设计中用作示范比特率。

如果 FPGA 正在接收比特率相同的多个异步比特流,就可以用 DCM 提供的两个全局时钟相位作为时钟来驱动所有比特流的过采样器。因此,这种技术对于接收比特率相同的多个比特流非常有效。

第 4 页图3 中的 DCM 不能在进行时钟乘法运算的同时提供两个相隔 90 度的时钟相位。因此,DCM 的输入端需要一个比特率时钟。不过,Virtex-5 器件时钟管理管道中的 PLL 可以同时对输入的时钟进行乘法运算并提供两个不同的时钟相位,并且允许使用较低频率的输入参考时钟。

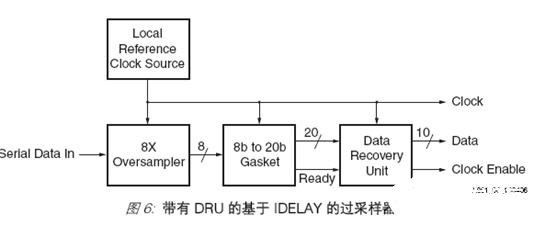

图6 所示为连接至 DRU 的基于 IDELAY 的过采样器设计。这种 DRU 支持 8 倍过采样,当初的开发目的是在 RocketIO 收发器上用作过采样器。由于这一原因,它预置一个 20 位的输入矢量,所以就需要少量接口逻辑将采样器的 8 位输出端与 DRU 的 20 位输入端衔接起来。DRU在其输出端口生成 10 位的恢复数据字,同时生成一个信号,一旦数据字生效则该信号被置位。DRU 还可以生成 20 位的输出字。