NET “rx_ce” TNM = RXCE;

TIMESPEC TS_RXCE = FROM RXCE TO RXCE BIT_CLK / 5;

位置约束

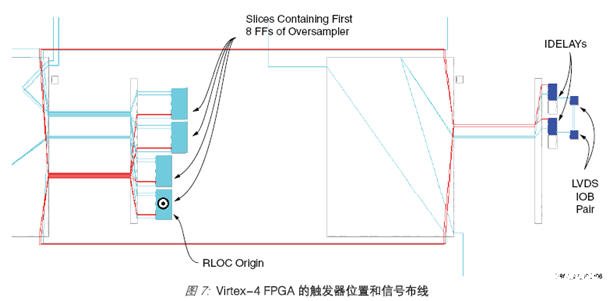

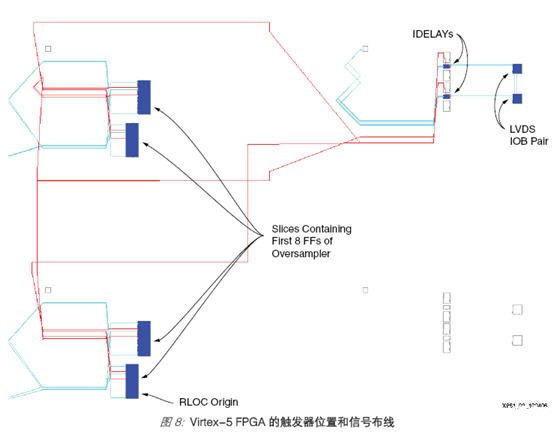

要从过采样器中获得良好性能,重要的是应将第一组的八个触发器(即直接从 IDELAY 基元输出端采集数据的触发器)放置在尽量靠近 IDELAY 基元处,并且从两个 IDELAY 基元到八个触发器的布线对于所有八个触发器来说应尽量相同。过采样器模块应设计成允许在约束文件中放置一个 RLOC 起点,以约束这第一组的八个触发器。应将 RLOC 起点设置成使触发器在 CLB中的位置尽可能紧靠 IDELAY 基元的左侧,因为这样放置可提供最直接的信号布线。如果不可能将触发器置于 IDELAY 基元的左侧,可以将其放在紧靠其右侧的位置,只是性能会稍有降低。

图7 所示为触发器紧靠 IDELAY 基元左侧的 Virtex-4 器件。图中以红色表示从两个 IDELAY 基元到触发器的数据信号布线。

XAPP861 (v1.0) 2006 年 10 月 13 日www.xilinx.com/cn 11

R 以下约束显示如何将设计中的两个 oversample_8x 模块分别指定给不同的 U_SET,以及如何对其指定 RLOC_ORIGIN 约束,以将其置于各自 IOB 的旁边。在本示例中,两个oversample_8x 模块的实例名分别为 OVRSAMPLE1 和 OVRSAMPLE2。

INST “OVRSAMPLE1” U_SET=USET_OVR1;

INST “OVRSAMPLE1” RLOC_ORIGIN = X0Y24;

INST “OVRSAMPLE2” U_SET=USET_OVR2;

INST “OVRSAMPLE2” RLOC_ORIGIN = X50Y24;

结论

本文所述技术使用 Virtex-4 和 Virtex-5 器件中各 IOB 内置的 IDELAY 资源来实现用于异步串行比特流的高效高性能8倍过采样器。当用多个 DCM 生成时钟相位时,这种技术可以提供比多时钟相位法更高的采样精度。因为 IDELAY 资源可以为各比特流提供更多采样点,所以只需一个 DCM 和两个全局时钟即可提供对以同样比特率运行的任意数量的异步比特流进行 8 倍采样所需的所有时钟。

责任编辑:gt

关于可编程逻辑就介绍完了,您有什么想法可以联系小编。