今天小编要和大家分享的是可编程逻辑相关信息,接下来我将从以FPGA为核心的高速误码测试仪设计流程概述,直流电机寿命测试仪/ 电机测试仪/ 疲劳测试仪这几个方面来介绍。

可编程逻辑相关技术文章以FPGA为核心的高速误码测试仪设计流程概述

误码分析仪作为数字通信系统验收、维护和故障查询的理想工具,广泛应用于同轴电缆、光纤、卫星及局间中继等符合CEPT(European Confence of Postal and Telecommunications Administrations)数字系列通信系统传输质量的监测。评价一个通信系统的可靠性的指标就是检测该通信系统在数据传输过程中误码率的大小,本文设计的高速信号误码测试仪,用于对EPON中接收和发送突发光信号的接收模块的可靠性进行检测。目前误码分析仪的工作模式已发展到如下4种:分析仪模式、发生器模式、分析仪/发生器模式、直通模式。本设计中的误码测试仪属于第3种类型,即该误码测试仪可以产生测试的码流,又可以进行误码测试。

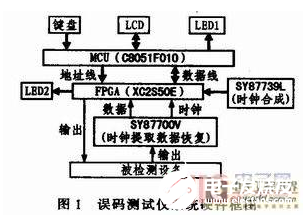

误码测试仪主要由发送模块,接收模块,显示模块,控制模块等几个模块组成,系统硬件结构框图如图1所示。其中发送、接收模块在FPGA中实现,控制模块由单片机实现,显示模块由单片机驱动,这样使得设计的误码分析仪具有体积轻巧,接口丰富,简单易用,成本低廉,内核可升级等特点。

1 基于FPGA的误码测试仪的设计

FPGA在该设计中实现了误码测试仪的核心功能,FPGA设计使用的是自顶向下模块化的设计方法。基于FPGA设计的模块包括:SY87739L频率计的控制模块、SY87700时钟提取控制模块、计数模块、伪随机序列发送模块、数据接收模块、与单片机的通信模块。

1.1 频率合成芯片SY87739L的控制模块

在设计中SY87739L合成的频率用于伪随机序列合成的同步时钟,因为该误码测试仪可以测试的频率有32 Mb/s、64 Mb/s、122 Mb/ s、155 Mb/s 4种。所以该芯片要根据设置的参数合成相应的频率。具体合成哪一个,由FPGA来实现对SY87739L的控制。

SY87739L(规程式透明3.3 V 10~729 MHz分数N合成器)是一个频率合成芯片。依照一参考频率源,它可以合成10~729 MHz范围内的差分频率。此外它可以精确地为标准的传输协议合成相应的参考频率。SY87739L合成的频率是由一个32位的串行输入的编程数据决定。PROGCS为高电平时,编程数据才会被SY87739L接收。若用户需要改变编程数据获得一个新的频率时,应先将PROGCS设置为高电平,延时一段时间(待32 bit编程数据被SY87739L接收)后在回落到低电平。既在PROGCS的下降沿时,SY87739L会由前一时段接收到32 bit编程数据决定合成新的频率。具体步骤如下:1)确定编程数据的值;2)设置PROGCS为高电平;3)串行输入32 bit编程数据(由PROGDI管脚输入),同时在PROGSK端输入时钟信号;4)设置PROGCS为低电平;5)等待LOCKED跳为高电平。