1.3 计数模块

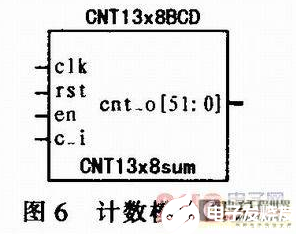

计数模块是用来计算总的码数和误码数以及误码块数的,该计数器是一个同步复位计数器。由verilog HDL代码综合出的图元如图6所示。

该计数模块最大的计数值达252,用Modelsim仿真软件对计数模块进行功能仿真的结果如图7所示:

在测试文件中,c_i赋值为一个脉冲流,在cnt_o输出的计数结果是正确的。可以判断出该模块的功能的正确性。

1.4 伪随机序列发送模块

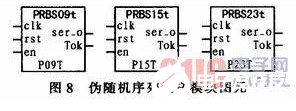

伪随机序列发送模块的任务是以SY87739L合成的频率为时钟产生伪随机序列并串行输出伪随机序列。该模块可以产生三种级数的伪随机序列,生成的伪随机序列串行输出。具体合成那一级数决定于washbone模块(FPGA与单片机的通信控制模块)输出的控制信号:P09T-en(合成9级m序列使能信号)、P15T-en(合成15级m序列使能信号)、P23T-en(合成23级m序列使能信号)。三个信号中哪个为高电平就合成相应级数的伪随机序列。由Verilog HDL代码综合出的图元如图8所示。

功能仿真结果(合成23级伪随机序列)如图9所示。

在测试文件中赋给该模块的输入信号相应的值,使其完成合成23级伪随机序列的功能。在上图中,ser_o串行输出23级的m序列,可以判断该模块可以成功的合成m序列实现误码测试仪发送端的功能。

1.5 数据接收模块

FPGA中的接收模块实现的功能有:1)m序列发生,2)是误码检测。前者的逻辑功能与发送端模块相类似,其作用是产生一个与发端码形相同并且比特对齐的本地m序列;后者的作用是将收到的数据与本地m序列相比较,检测是否有误码,若有误码则输出一个误码脉冲给计数模块进行统计。该模块可以接收三种级数的伪随机序列,由Verilog程序综合出的图元如图10所示。