将执行模块划分为:顶层模块、操作1模块、操作2模块、操作3模块、功能执行模块、异常处理模块。顶层模块实现3种操作的数据与指令分流和中间变量的处理;操作1模块实现寄存器旁路的功能和数据的处理;操作2模块和操作3模块实现的功能与操作1模块相同,不同点在于中间数据冲突处理不一样;功能执行模块实现16种操作的具体功能;异常处理模块实现数据或指令的异常处理的具体功能。将各个模块连接就实现执行单元的整个功能。

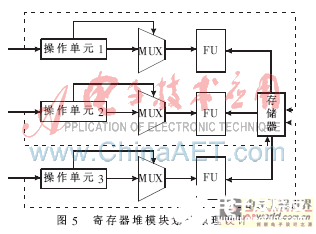

2.4 寄存器堆的实现

寄存器堆的结构如图5所示。输入端的数据、指令是来自2个单元,一个是取指令单元数据和指令,另一个是写回单元的数据;输出的指令、数据要传输到执行单元中进行执行操作。因为3种操作是并行执行的,每一种操作功能都是一样,因此在某个输入信号下,经由某种操作单元时,在选择器MUX下,选择某种具体操作运算。在功能单元FU中,对取出的存储器数据进行相应的操作运算处理,并将操作处理的结果输出送到执行单元中。图中虚线表示将写回单元输送来的操作数据直接存储到存储器中。实现时,要注意处理数据的相关问题。

2.5 写回单元的设计

写回单元是VLIW微处理器的最后一个单元,它的功能是将执行单元的操作结果写回到寄存器堆中,并在读有效的情况下,输出相应的操作处理数据。该模块设计相对比较简单,要实现写回寄存器堆的数据和该数据的目标寄存器地址,以及读出处理单元的操作处理数据。

2.6 综合仿真与测试

将上述所设计的模块,运用原理图的设计方法,按图2 VLIW微处理模块划分结构进行相应的连接,并选择相应的器件进行编译测试,其仿真测试功能波形如图6所示。图中的波形图添加了中间变量寄存器的波形图,以便能够更好地对比输出波形,分析处理器功能。VLIW微处理器首先将要处理的数据装入寄存器中,利用寄存器寻址的方式,对数据进行相应的16种功能操作运算,然后利用读的功能读出操作处理的数据结果。

在图6中,添加的中间变量是寄存器地址,基本的输入有时钟信号、复位信号、指令、数据。复位信号为低电平时,电路处于有效的工作状态,输出相关的操作数据。运用装载指令对寄存器依次装入数据,在下一个时钟脉冲时,对寄存器的数据进行读出操作,输出数据有效信号输出高电平。