今天小编要和大家分享的是可编程逻辑相关信息,接下来我将从基于FPGA和NAND Flash的便携式高速信号采集系统的设计方案介绍,powerlab生理信号采集系统这几个方面来介绍。

可编程逻辑相关技术文章基于FPGA和NAND Flash的便携式高速信号采集系统的设计方案介绍

0 引言

随着现代检测技术和科技水平的高速发展,信号采集技术的应用范围越来越广泛[1]。与此同时,对信号采集系统的采集精度、采样率以及便携性等设计需求提出了更高的要求。现场可编程门阵列(FPGA)具有逻辑门充足、时钟频率高、速度快、效率高和IP核丰富等特点,使其成为高速信号采集系统设计的一个有效手段[2-3]。针对当前信号采集系统的设计需求,本文主要介绍如何提高信号采集系统的采样率和便携性。

目前,信号便携式信号采集系统采样率低主要受限于信号采集系统的传输速度和处理速度不足。查阅近几年的相关文献,基于FPGA的信号采集系统主要有以下两种设计方案:方案一,采用FPGA作为逻辑控制模块,搭配ADC采集模块和USB2.0传输模块[4];方案二,同样采用FPGA作为逻辑控制模块,搭配DDR2/DDR3模块对ADC模块采集的数据进行高速缓存[5-6]。方案一受限于USB的传输速度其采样率较低[7-8];方案二虽然可以达到较高的采样率,但是具有数据易失、存储容量小的问题,便携性不足[9]。

针对以上问题,本文结合目前NAND Flash高速存储的特性,提出了便携式高速信号采集系统的设计方案。该设计的关键在于利用存储芯片写入速度快、数据总线可复用等特点,使ADC采集到的信号采用DMA方式存入存储芯片中。其次,该设计配置LCD显示屏,用于信号的实地查看,减少了上位机的配置。系统满足长时间、多批次的信号采集。

1 系统总体设计方案

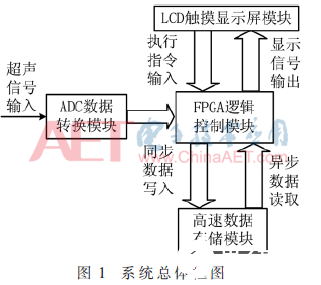

根据功能和原理,该系统分为4个模块:基于FPGA芯片的逻辑控制模块、以ADC芯片为主的数据转换模块、以NAND_Flash芯片为核心的高速数据存储模块以及LCD触摸显示屏模块,如图1所示。

系统基本工作原理:首先,模数转换模块在接收到模拟信号后,将信号转换为数字信号并发送到FPGA逻辑控制模块中的FIFO中;其次,FPGA逻辑控制模块采用直接存储器存储(Direct Memory Access,DMA)模式将数据从FIFO中传递到NAND_Flash数据存储模块;然后,NAND_Flash模块结合其相应的内部结构以同步的方式进行高速数据存储;最后,将由LCD模块发送相应的指令,以一定速度读取数据,经过FPGA进行一定的信号处理,在LCD显示屏中显示。