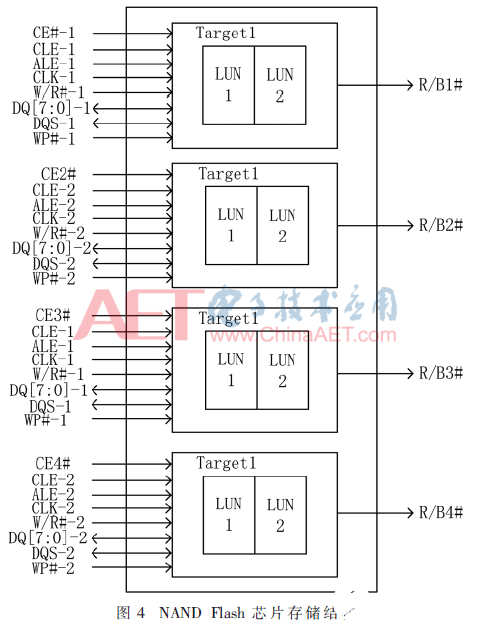

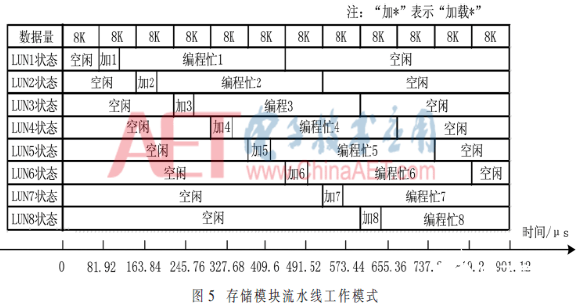

针对这一问题,本设计结合MT29F256G08AUCABH3的存储结构特点,如图4所示。该芯片内部具有8个LUN结构,且当一个LUN处于编程状态时,其他LUN可以进行读写以及编程。根据这一特性,本设计将其内部的8个LUN芯片采用流水线方式排列,依次进行数据的存储操作,如图5所示。当采集数据达到8 KB,处于写准备状态的LUN开始以DDR方式进行数据写入。完成1页数据(8 KB)的写入后,后一LUN进入写准备状态,等待未存储数据再次达到8 KB。以此方式进行循环,当第8个LUN完成写操作时,第一个LUN完成编程过程,处于空闲状态可以进行写操作,图5所示为存储芯片流水线工作模式。

2.4 显示模块

在系统的显示模块,选用一款具有800×480分辨率和数字接口驱动的7英寸LCD液晶显示屏。显示屏的输出色彩信号通过565的RGB并口数字信号传输,搭配容量为512 MB的DDR2 SDRAM芯片用于缓存显示数据。系统显示模块的时钟频率为33 MHz。

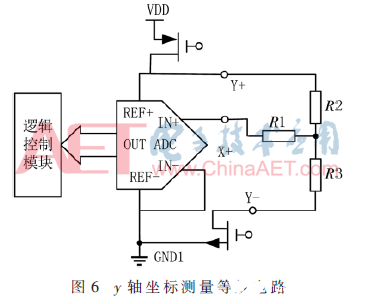

除显示功能外,该模块同时肩负人机交互功能。利用触摸屏的特性,完成对整个系统的操作控制,减少键盘模块,使操作更加简单。本设计采用电阻式触摸屏,屏幕的x轴和y轴各有两条信号线连接到触摸屏专用AD芯片上(本设计选择AW2083芯片),每次按触摸屏时,会在对应的x轴和y轴产生一个阻值。在两条坐标轴的正负极之间加参考电压,当其中一条坐标轴的某一位置被触按,则这个位置和对应坐标轴的正负极之间的电阻会通过电压的形式反馈给ADC的输入端,产生12 bit的AD量化值,AD芯片采集到的坐标数据与实际坐标值成正比,且为线性关系。图6所示为y轴坐标测量等效电路图。

3 系统程序逻辑设计

当系统上电后,系统进行初始化操作。FPGA读取配置NAND Flash芯片中系统的配置信息。获取显示模块的初始化界面并进行输出和显示,同时从配置芯片中获取存储模块下一存储地址。系统初始化完毕后,系统进入待机状态,并监听LCD显示模块的指令输入。

3.1 信号采集流程

通过点击LCD模块中的“开始采集”按钮,触发信号采集程序。逻辑控制模块监听到信号采集开始指令,系统进入信号采集流程。